# **MECL Data**

**ON Semiconductor**

# **MECL Data**

DL122/D Rev. 7, Mar–2000

© SCILLC, 2000 Previous Edition © 1996 "All Rights reserved"

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

North America Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

**German Phone:** (+1) 303–308–7140 (M–F 2:30pm to 5:00pm Munich Time)

Email: ONlit-german@hibbertco.com

ench Phone: (+1) 303–308–7141 (M–F 2:30pm to 5:00pm Toulouse Time)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (M–F 1:30pm to 5:00pm UK Time)

Email: ONlit@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

**Phone**: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong 800-4422-3781

Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–8549

Phone: 81–3–5487–8345 Email: r14153@onsemi.com

Fax Response Line: 303-675-2167

800-344-3810 Toll Free USA/Canada

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.

This book presents technical data for a broad line of MECL integrated circuits. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, selector guides are included to simplify the task of choosing the best combination of circuits for optimum system architecture. For the most up-to-date information, please visit our website at: http://onsemi.com

ECLinPS, ECLinPS Lite, MECL, MECL 10H, MECL 10K, MECL III, MTTL, and ON–Demand CDROM are a trademarks of Semiconductor Components Industries, LLC.

MOSAIC is a trademark of Motorola, Inc.

The brands and product names mentioned are trademerks or registered trademarks of their respective holders.

# **Table of Contents**

| Deleted Devices                          | System Design Considerations 29    |

|------------------------------------------|------------------------------------|

| Listing of Deleted Devices 5             | Thermal Management                 |

| End-of-Life Devices (EOL)                | Thermal Effects on Noise Margin 33 |

| Listing of EOL Devices                   | Mounting and Heatsink              |

| Numeric Data Sheet Listing               | Applications Assistance Form       |

| MECL 10H                                 | Chapter 2. MECL 10H Data Sheets    |

| Carrier Band Modem 9                     | MECL 10H Selector Guide 41         |

| Ol and an A. O an anal line forms of the | MECL 10H Introduction              |

| Chapter 1. General Information           | MECL 10H Data Sheets 45            |

| High-Speed Logic                         | Chapter 3. MECL 10K Data Sheets    |

| MECL Family Comparison                   | MECL 10K Selector Guide            |

| Basic Design Considerations              | MECL 10K Data Sheets               |

| Pin Conversion Tables                    | Chapter 4. Carrier Band Modem      |

| Technical Data                           | Carrier Band Modem Data Sheet 437  |

| General Characteristics                  | Chapter 5. Ordering Information    |

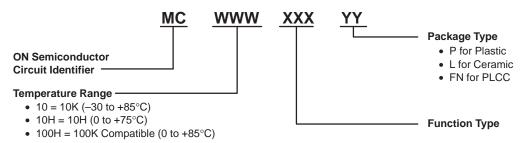

| Switching Parameters                     | Device Nomenclature 461            |

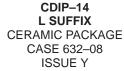

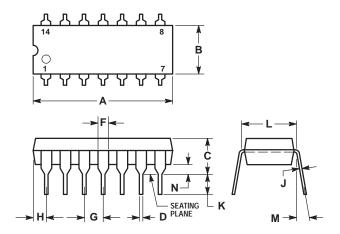

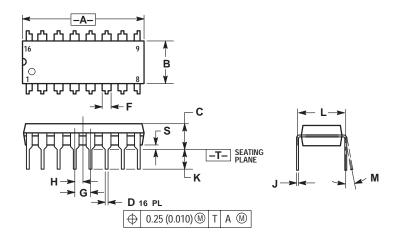

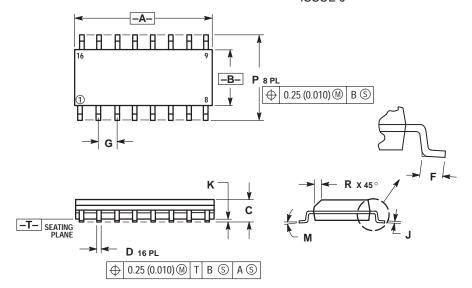

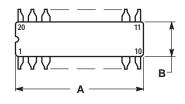

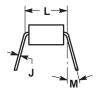

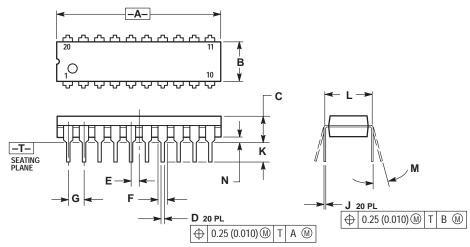

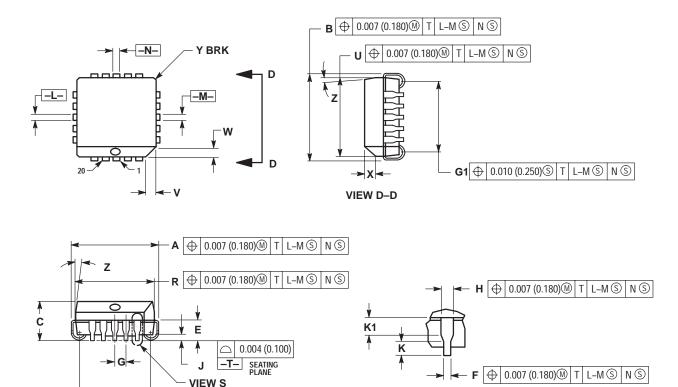

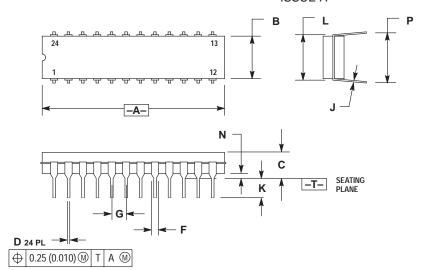

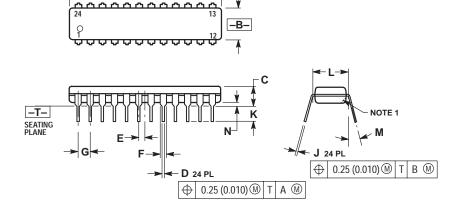

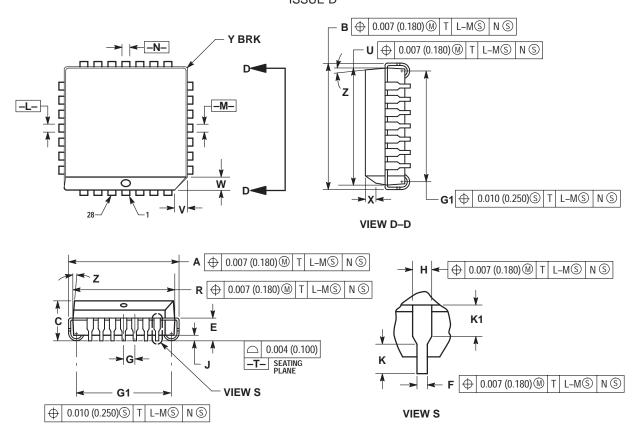

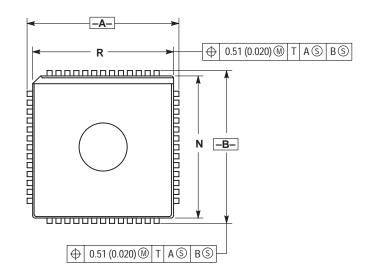

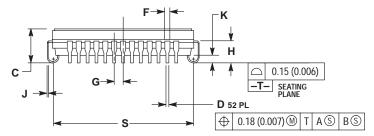

| Setup and Hold                           | Case Outlines 462                  |

| Testing MECL 10H, 10K and III            | ON Semiconductor Worldwide         |

| Operational Data                         | Sales Offices                      |

## **Deleted Devices**

The following list of devices have been deleted since the last publication of this book.

#### **DATA SHEETS DELETED**

| MC10137 | MC1648 | MC1650 | MC1651 |  |

|---------|--------|--------|--------|--|

| MC1658  | MC1660 | MC1662 | MC1670 |  |

| MC1692  |        |        |        |  |

# **End-of-Life (EOL) Devices**

The following list of devices have been placed on EOL and are not recommended for new designs, since the last publication of this book.

| <b>END</b> | OF | LIFE | DEV | ICES |

|------------|----|------|-----|------|

|------------|----|------|-----|------|

MC10H145

MC10H660

# **Numeric Data Sheet Listing**

| MECL 10H Data | Sheets                                            |

|---------------|---------------------------------------------------|

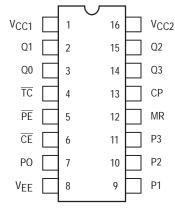

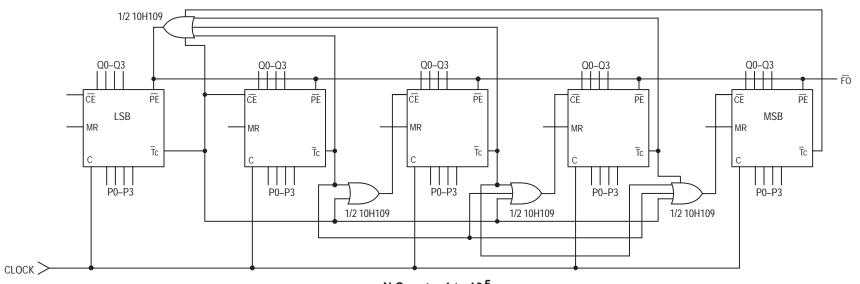

| MC10H016      | 4–Bit Binary Counter                              |

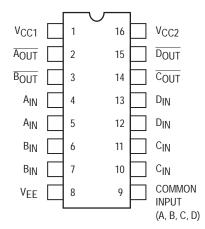

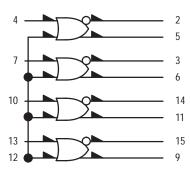

| MC10H100      | Quad 2-Input NOR Gate With Strobe                 |

| MC10H101      | Quad OR/NOR Gate                                  |

| MC10H102      | Quad 2-Input NOR Gate                             |

| MC10H103      | Quad 2-Input OR Gate                              |

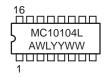

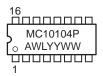

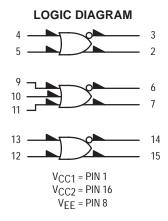

| MC10H104      | Quad 2-Input AND Gate                             |

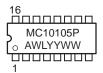

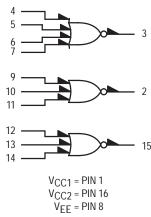

| MC10H105      | Triple 2–3–2–Input OR/NOR Gate                    |

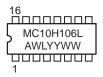

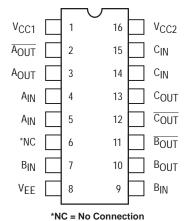

| MC10H106      | Triple 4–3–3–Input NOR Gate                       |

| MC10H107      | Triple 2–Input Exclusive OR/Exclusive NOR Gate    |

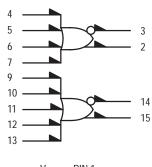

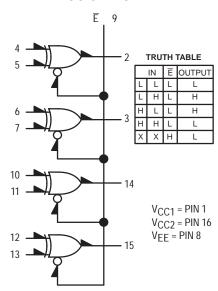

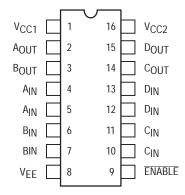

| MC10H109      | Dual 4–5–Input OR/NOR Gate                        |

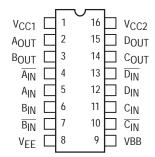

| MC10H113      | Quad Exclusive OR Gate                            |

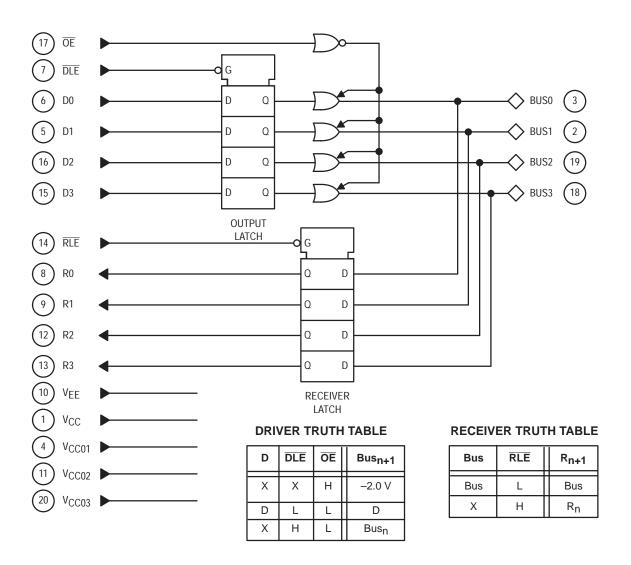

| MC10H115      | Quad Line Receiver                                |

| MC10H116      | Triple Line Receiver                              |

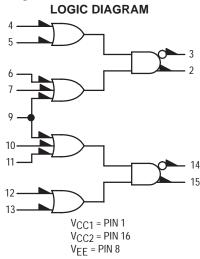

| MC10H117      | Dual 2–Wide 2–3–Input OR–AND/OR–AND Gate          |

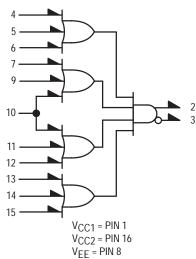

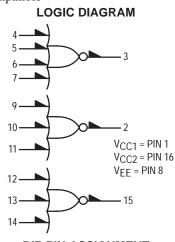

| MC10H121      | 4-Wide OR-AND/OR-AND Gate                         |

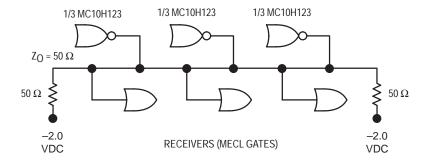

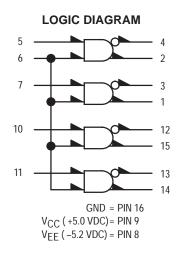

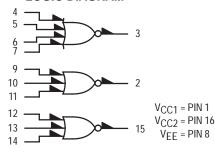

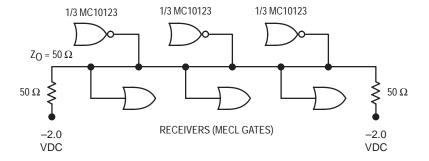

| MC10H123      | Triple 4–3–3–Input Bus Driver         76          |

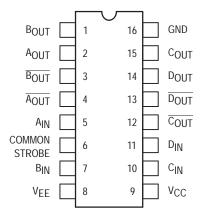

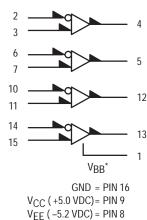

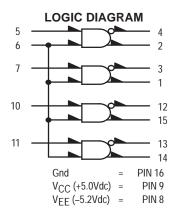

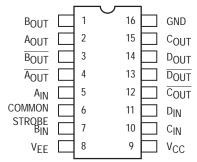

| MC10H124      | Quad TTL-to-MECL Translator With TTL Strobe Input |

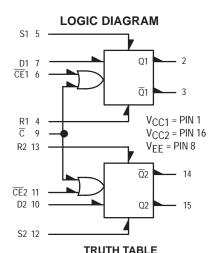

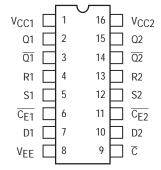

| MC10H125      | Quad MECL-to-TTL Translator                       |

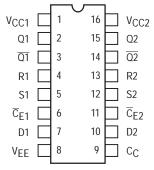

| MC10H130      | Dual Latch 82                                     |

| MC10H131      | Dual D Type Master–Slave Flip–Flop                |

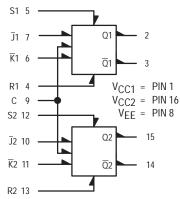

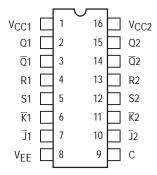

| MC10H135      | Dual J–K Master–Slave Flip–Flop                   |

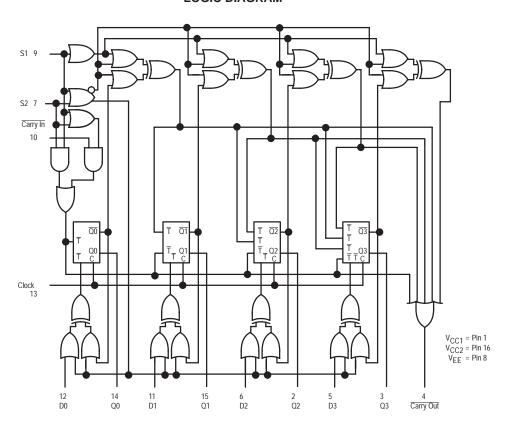

| MC10H136      | Universal Hexadecimal Counter                     |

| MC10H141      | Four–Bit Universal Shift Register                 |

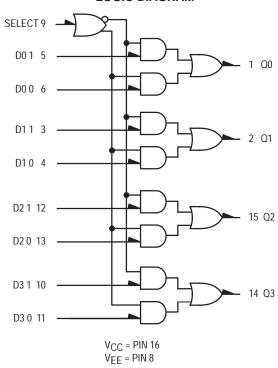

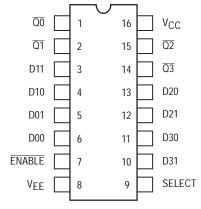

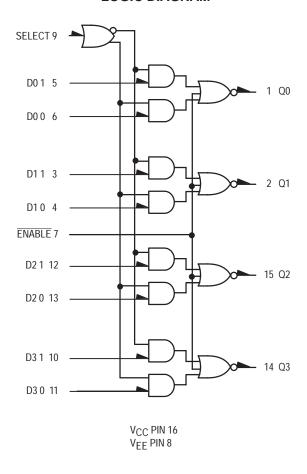

| MC10H158      | Quad 2-Input Multiplexer                          |

| MC10H159      | Quad 2-Input Multiplexer                          |

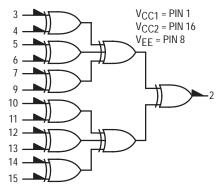

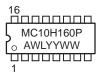

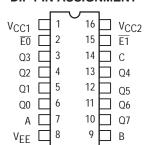

| MC10H160      | 12-Bit Parity Generator-Checker                   |

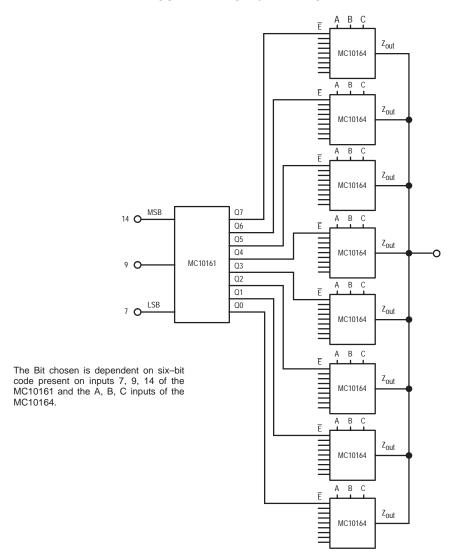

| MC10H161      | Binary to 1–8 Decoder (Low)                       |

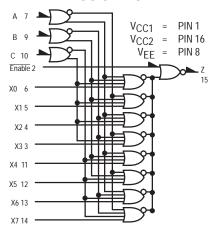

| MC10H162      | Binary to 1–8 Decoder (High)                      |

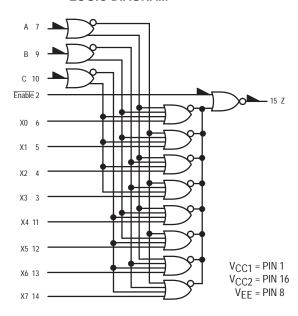

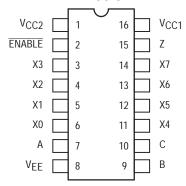

| MC10H164      | 8-Line Multiplexer                                |

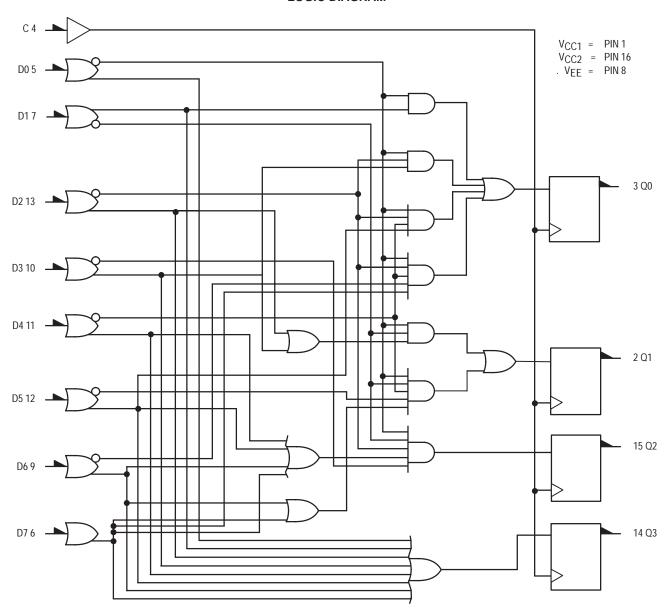

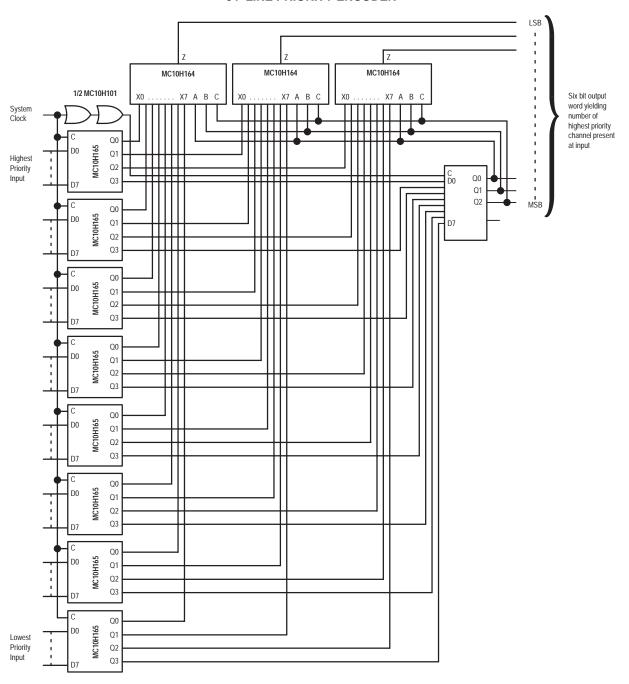

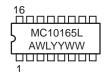

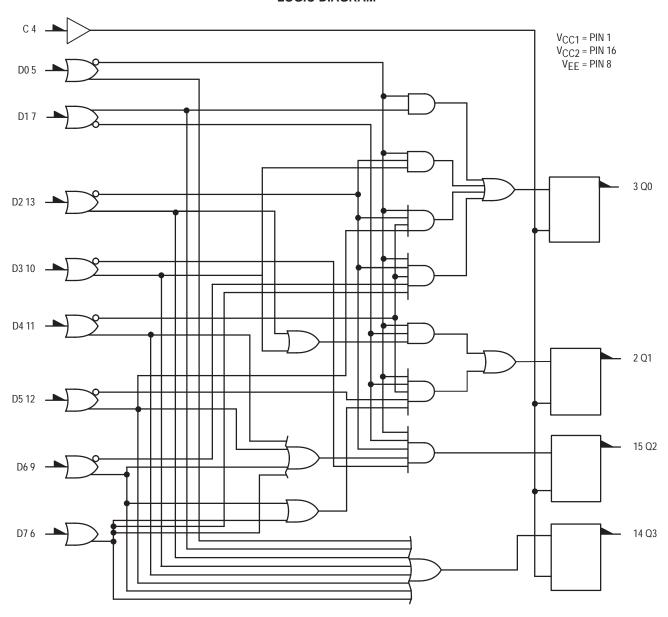

| MC10H165      | 8-Input Priority Encoder                          |

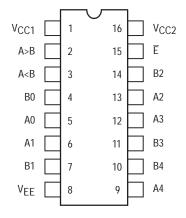

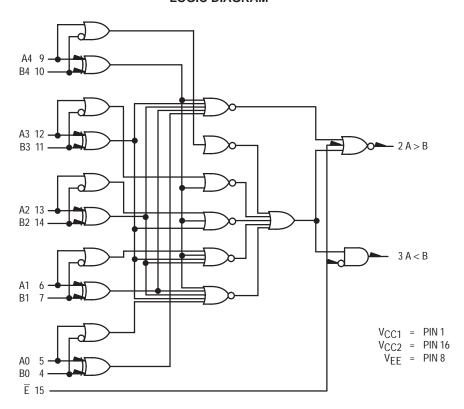

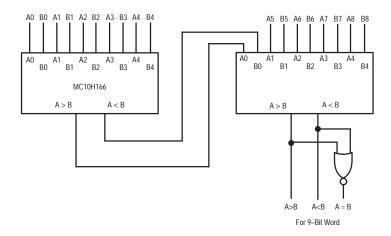

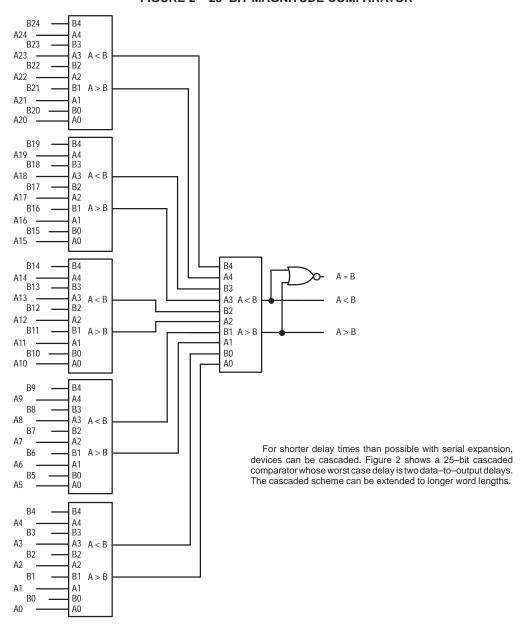

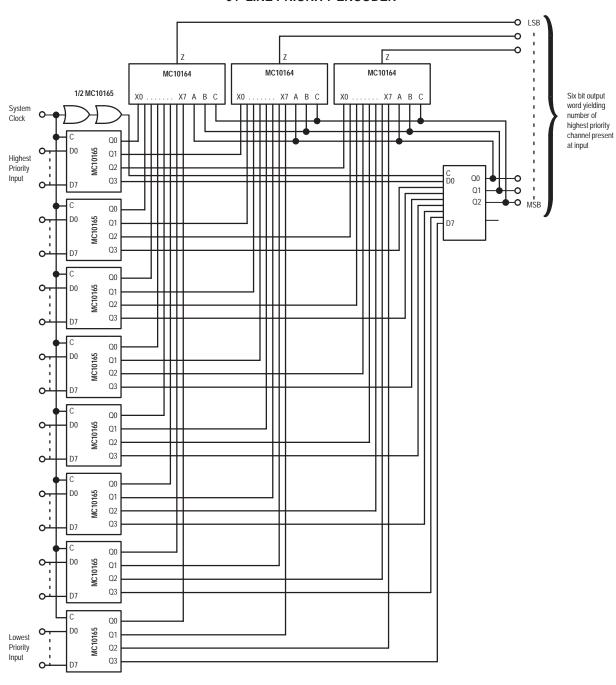

| MC10H166      | 5-Bit Magnitude Comparator                        |

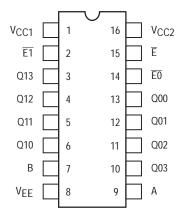

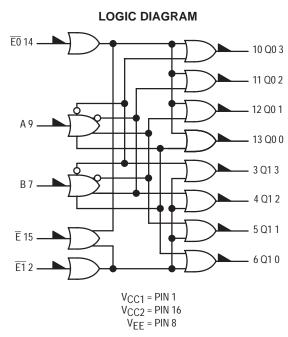

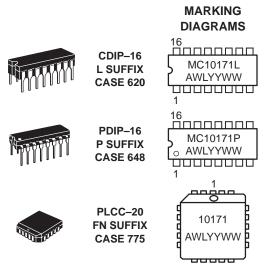

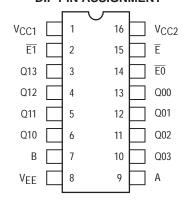

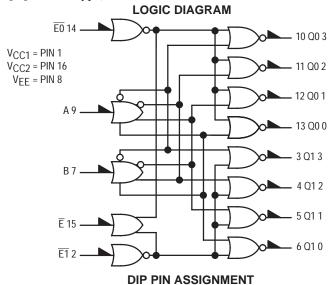

| MC10H171      | Dual Binary to 1–4 Decoder (Low)                  |

| MC10H172      | Dual Binary to 1–4–Decoder (High)                 |

| MC10H173      | Quad 2-Input Multiplexer/ Latch                   |

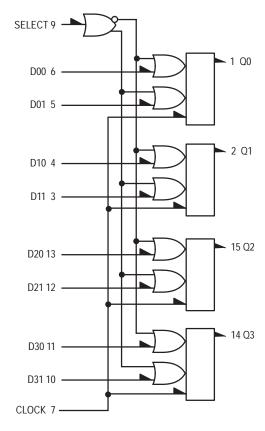

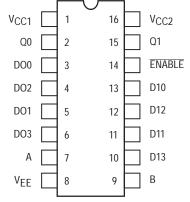

| MC10H174      | Dual 4 to 1 Multiplexer                           |

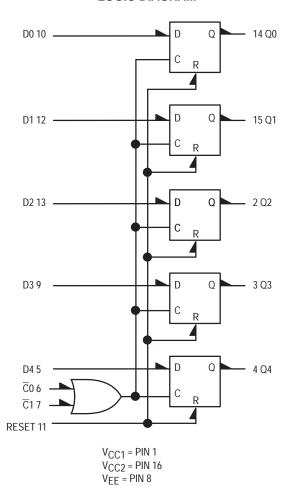

| MC10H175      | Qunit Latch                                       |

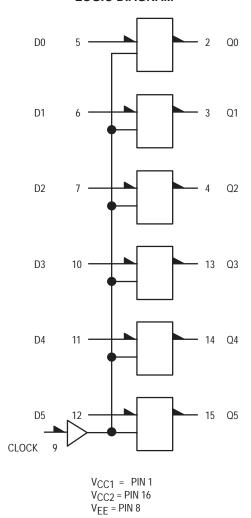

| MC10H176      | Hex D Master–Slave Flip–Flop                      |

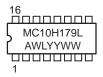

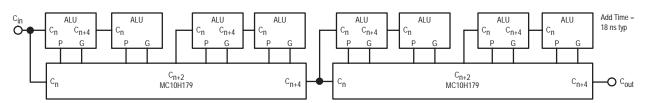

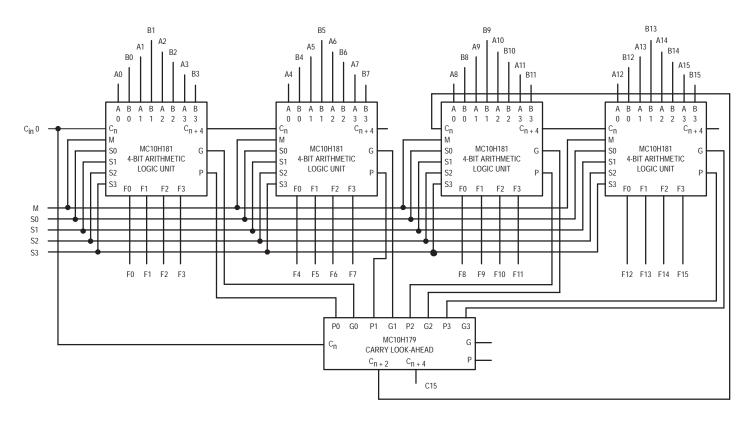

| MC10H179      | Look-Ahead Carry Block                            |

| MECL 10H Dat | a Sheets                                                    |

|--------------|-------------------------------------------------------------|

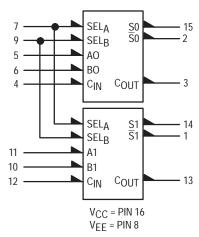

| MC10H180     | Dual 2–Bit Adder/Subtractor                                 |

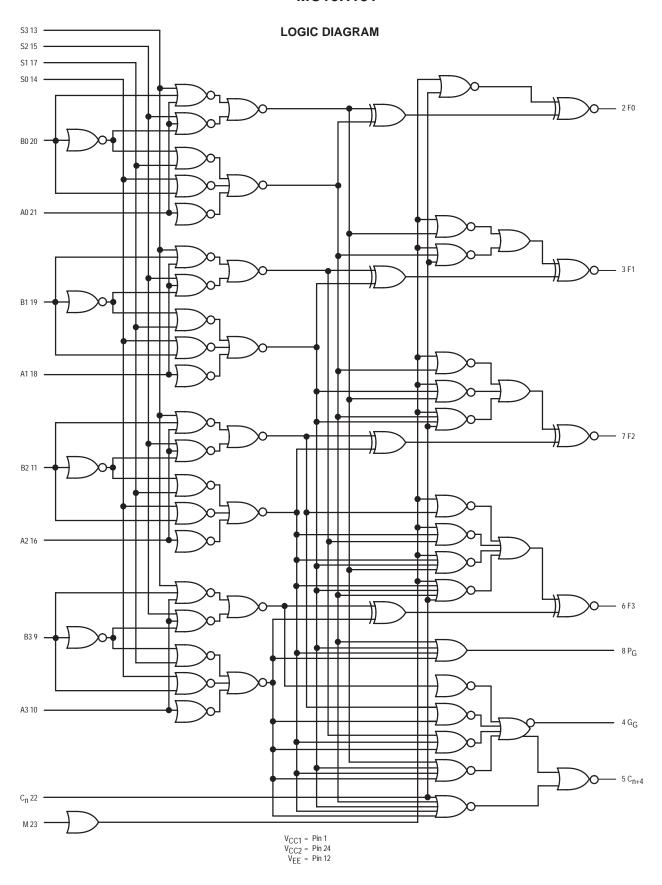

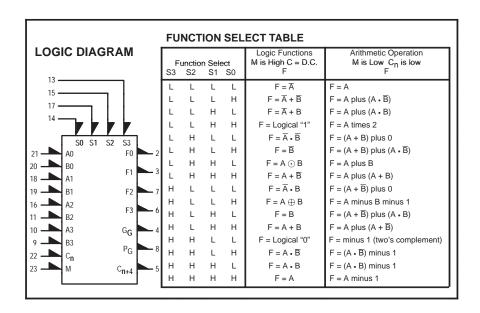

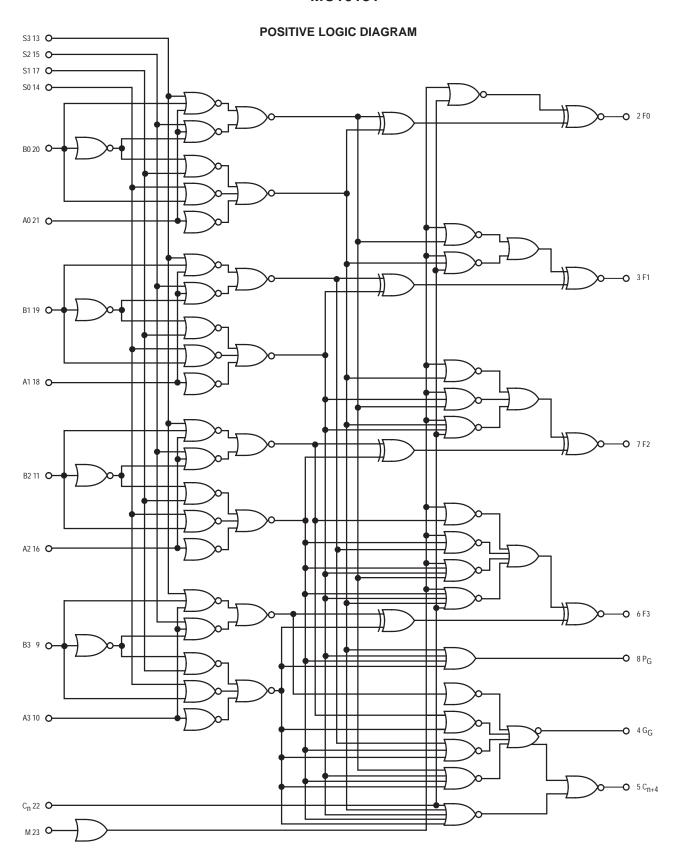

| MC10H181     | 4-Bit Arithmetic Logic Unit/ Function Generator             |

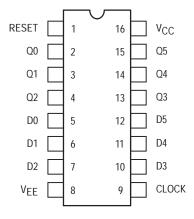

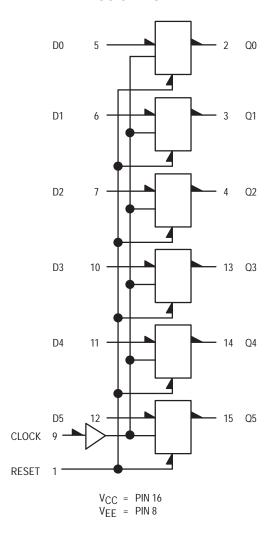

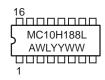

| MC10H186     | Hex D Master–Slave Flip–Flop with Reset                     |

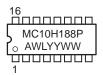

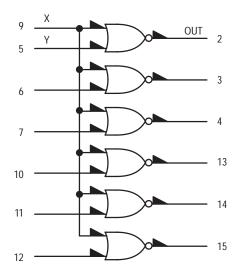

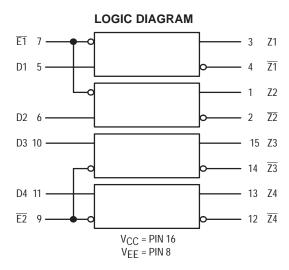

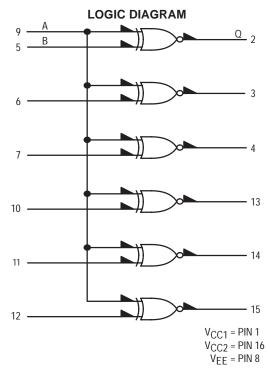

| MC10H188     | Hex Buffer with Enable                                      |

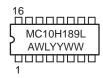

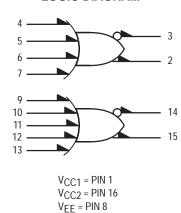

| MC10H189     | Hex Inverter with Enable                                    |

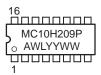

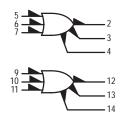

| MC10H209     | Dual 4–5–Input OR/NOR Gate                                  |

| MC10H210     | Dual 3-Input 3-Output OR Gate                               |

| MC10H211     | Dual 3-Input 3-Output NOR Gate                              |

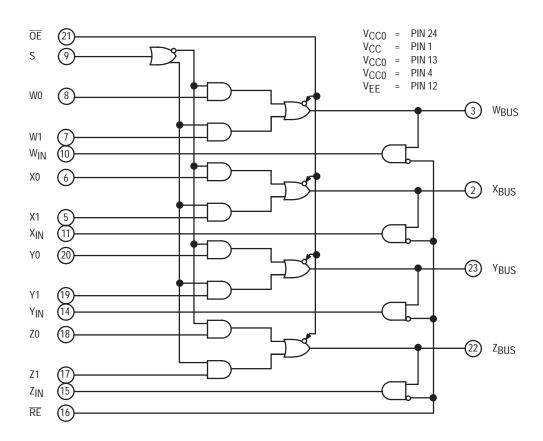

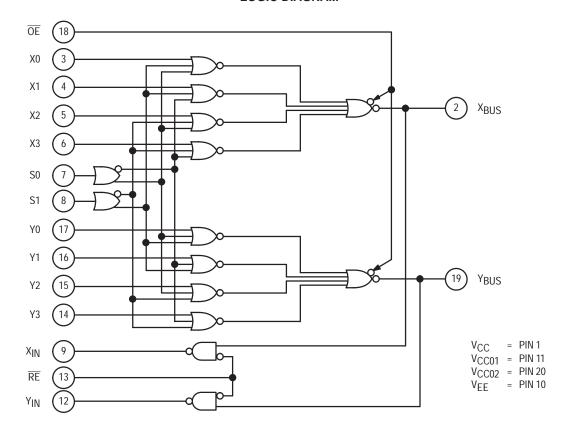

| MC10H330     | Quad Bus Driver/Receiver with 2-to-1 Output Multiplexers    |

| MC10H332     | Dual Bus Driver/Receiver with 4-to-1 Output Multiplexers    |

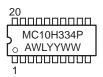

| MC10H334     | Quad Bus Driver/Receiver with Transmit and Receiver Latches |

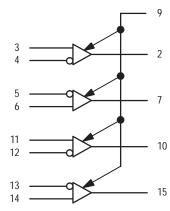

| MC10H350     | PECL* to TTL Translator                                     |

| MC10H351     | Quad TTL/NMOS to PECL* Translator                           |

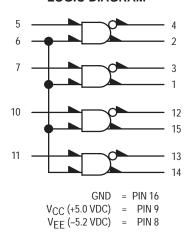

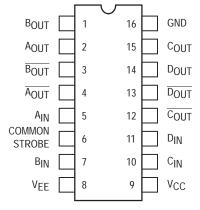

| MC10H352     | Quad CMOS to PECL* Translator                               |

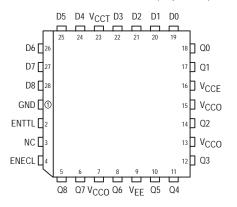

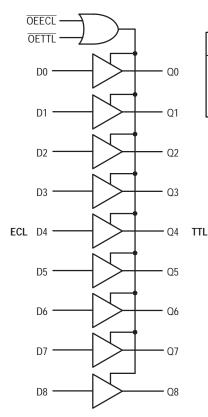

| MC10H424     | Quad TTL to ECL Translator with ECL Strobe                  |

| MC10/100H600 | 9-Bit TTL/ECL Translator                                    |

| MC10/100H601 | 9-Bit ECL/TTL Translator                                    |

| MC10/100H602 | 9-Bit Latch TTL/ECL Translator                              |

| MC10/100H603 | 9-Bit Latch ECL/TTL Translator                              |

| MC10/100H604 | Registered Hex TTL/ECL Translator                           |

| MC10/100H605 | Registered Hex ECL/TTL Translator                           |

| MC10/100H606 | Registered Hex TTL/PECL Translator                          |

| MC10/100H607 | Registered Hex PECL/TTL Translator                          |

| MC10/100H640 | 68030/040 PECL-TTL Clock Driver                             |

| MC10/100H641 | Single Supply PECL-TTL 1:9 Clock Distribution Chip          |

| MC10/100H642 | 68030/040 PECL-TTL Clock Driver                             |

| MC10/100H643 | Dual Supply ECL-TTL 1:8 Clock Driver                        |

| MC10/100H644 | 68030/040 PECL-TTL Clock Driver                             |

| MC10H645     | 1:9 TTL Clock Driver                                        |

| MC10/100H646 | PECL/TTL-TTL 1:8 Clock Distribution Chip                    |

| MC10/100H680 | 4-Bit Differential ECL Bus/TTL Bus Transceiver              |

| MC10/100H681 | Hex ECL/TTL Transceiver with Latches                        |

| MECL 10K Dat | a Sheets                                                    |

| MC10101      | Quad OR/NOR Gate                                            |

| MC10102      | Quad 2-Input NOR Gate                                       |

| MC10103      | Quad 2–Input OR Gate                                        |

| MC10104      | Quad 2–Input AND Gate                                       |

| MC10105      | Triple 2–3–2–Input OR/NOR Gate                              |

| MC10106      | Triple 4–3–3–Input NOR Gate                                 |

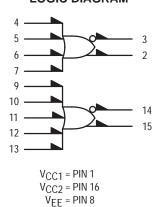

| MC10107      | Triple 2–Input Exclusive OR/ Exclusive NOR Gate             |

|              |                                                             |

### **MECL 10K Data Sheets**

| MC10109 | Dual 4–5–Input OR/NOR Gate                      | 260 |

|---------|-------------------------------------------------|-----|

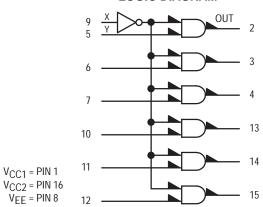

| MC10110 | Dual 3-Input/3-Output OR Gate                   | 263 |

| MC10111 | Dual 3-Input/3-Output NOR Gate                  | 266 |

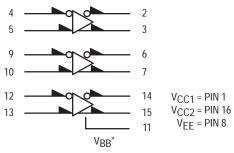

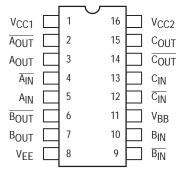

| MC10113 | Quad Exclusive OR Gate                          | 269 |

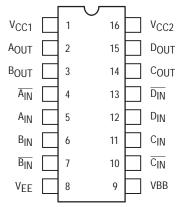

| MC10114 | Triple Line Receiver                            | 272 |

| MC10115 | Quad Line Receiver                              | 276 |

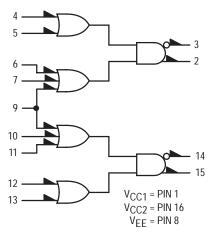

| MC10116 | Triple Line Receiver                            | 278 |

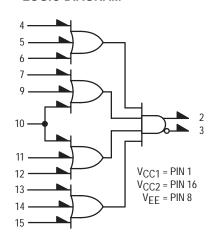

| MC10117 | Dual 2-Wide 2-3-Input OR-AND/OR-AND Gate        | 281 |

| MC10121 | 4-Wide OR-AND/OR-AND Gate                       | 284 |

| MC10123 | Triple 4–3–3–Input Bus Driver                   | 287 |

| MC10124 | Quad TTL to MECL Translator                     | 289 |

| MC10125 | Quad MECL to TTL Translator                     | 294 |

| MC10129 | Quad Bus Receiver                               | 299 |

| MC10131 | Dual Type D Master–Slave Flip–Flop              | 306 |

| MC10133 | Quad Latch                                      | 309 |

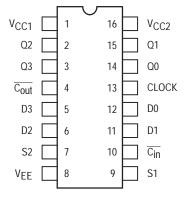

| MC10134 | Dual Multiplexer With Latch                     | 312 |

| MC10135 | Dual J–K Master–Slave Flip–Flop                 | 315 |

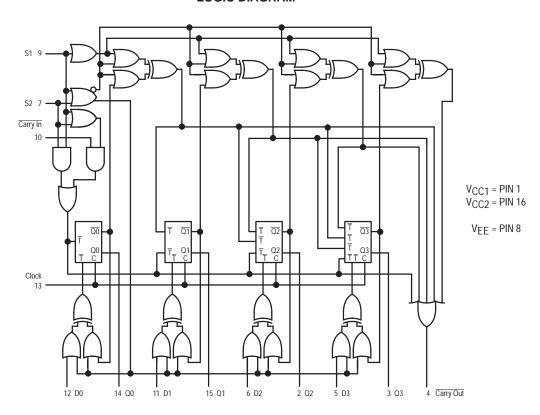

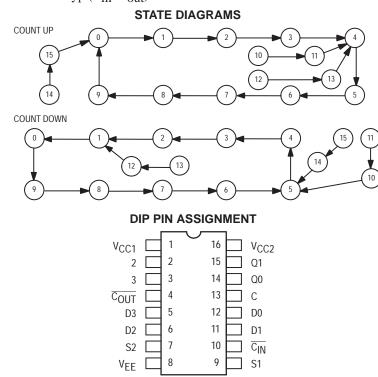

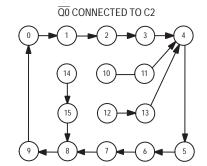

| MC10136 | Universal Hexadecimal Counter                   | 318 |

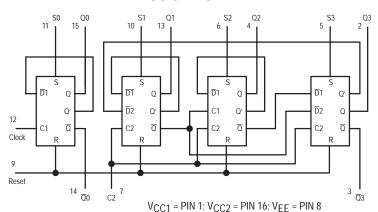

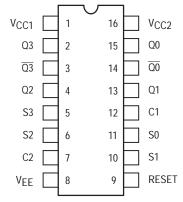

| MC10138 | Bi-Quinary Counter                              | 329 |

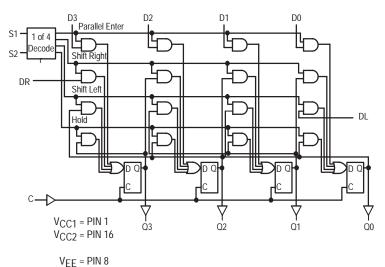

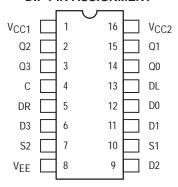

| MC10141 | Four Bit Universal Shift Register               | 333 |

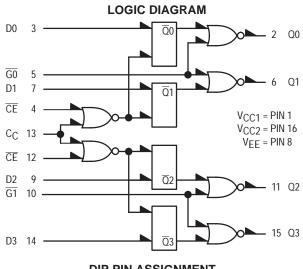

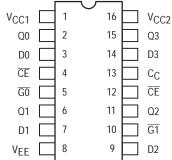

| MC10153 | Quad Latch                                      | 337 |

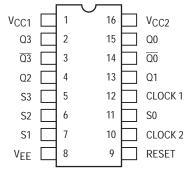

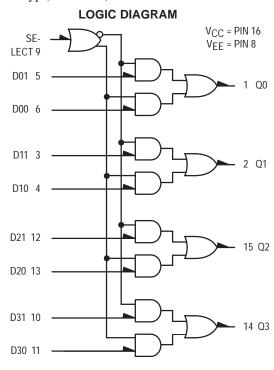

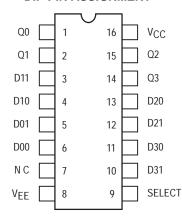

| MC10154 | Binary Counter                                  | 340 |

| MC10158 | Quad 2-Input Multiplexer                        | 343 |

| MC10159 | Quad 2-Input Multiplexer                        | 345 |

| MC10160 | 12-Bit Parity Generator-Checker                 | 347 |

| MC10161 | Binary to 1–8 Decoder (Low)                     | 350 |

| MC10162 | Binary to 1–8 Decoder (High)                    | 353 |

| MC10164 | 8-Line Multiplexer                              | 355 |

| MC10165 | 8-Input Priority Encoder                        | 358 |

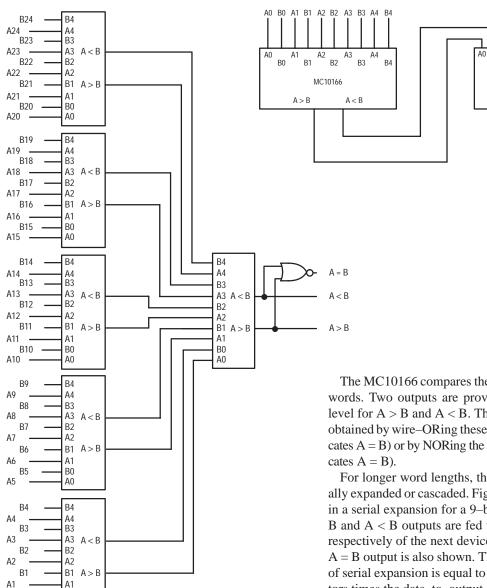

| MC10166 | 5-Bit Magnitude Comparator                      | 363 |

| MC10168 | Quad Latch                                      | 367 |

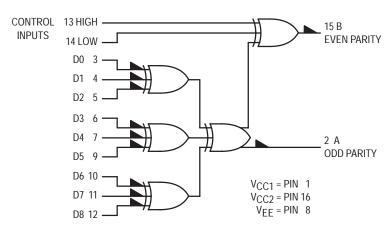

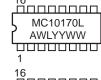

| MC10170 | 9+2-Bit Parity Generator/ Checker               | 370 |

| MC10171 | Dual Binary to 1–4 Decoder (Low)                | 373 |

| MC10172 | Dual Binary to 1–4 Decoder (High)               | 376 |

| MC10173 | Quad 2-Input Multiplexer/ Latch                 | 379 |

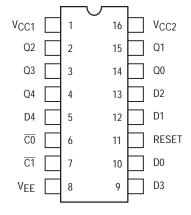

| MC10174 | Dual 4 to 1 Multiplexer                         | 382 |

| MC10175 | Quint Latch                                     | 384 |

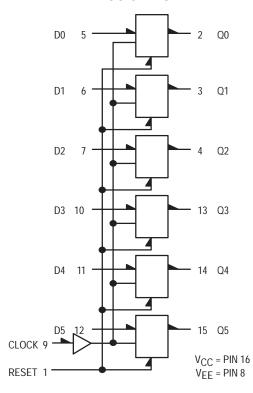

| MC10176 | Hex D Master/Slave Flip-Flop                    | 387 |

| MC10178 | Binary Counter                                  | 390 |

| MC10181 | 4-Bit Arithmetic Logic Unit/ Function Generator | 393 |

| MC10186 | Hex D Master–Slave Flip–Flop With Reset         | 398 |

|         |                                                 |     |

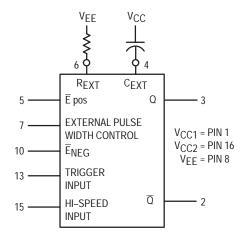

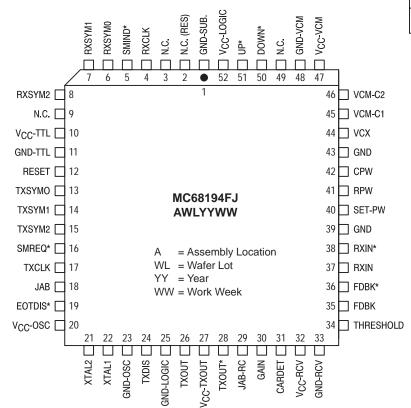

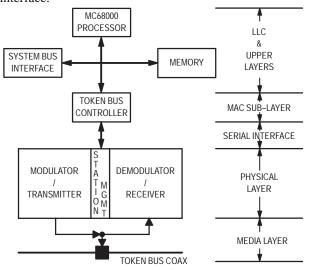

#### **MECL 10K Data Sheets** MC10188 Hex Buffer With Enable ..... 401 MC10189 403 MC10192 Quad Bus Driver ..... 405 MC10195 Hex Inverter/Buffer ..... 407 MC10197 Hex AND Gate ..... 409 MC10198 Monostable Multivibrator ..... 411 Dual 3-Input/3-Output OR Gate ..... MC10210 420 MC10211 Dual 3-Input/3-Output NOR Gate ..... 423 MC10212 High Speed Dual 3-Input/ 3-Output OR/NOR Gate ..... 426 MC10216 High Speed Triple Line Receiver ..... 429 High Speed Dual Type D Master-Slave Flip-Flop ..... MC10231 432 **Carrier Band Modem Data Sheet** MC68194 Carrier Band Modem (CBM) ..... 437

# CHAPTER 1 General Information

| High-Speed Logic 1                        |

|-------------------------------------------|

| MECL Products                             |

| MECL Family Comparison                    |

| Basic Design Considerations               |

| Definitions of Symbols & Abbreviations 15 |

| Pin Conversion Tables                     |

| MECL Positive and Negative Logic 19       |

| Technical Data                            |

| General Characteristics                   |

| Noise Margin                              |

| Switching Parameters                      |

| Setup and Hold                            |

| Testing MECL 10H and 10K                  |

| Operational Data                | _ |

|---------------------------------|---|

| System Design Considerations    | 2 |

| Thermal Management              | 2 |

| Optimizing Reliability          | 3 |

| Thermal Effects on Noise Margin | 3 |

| Mounting and Heatsink           | 3 |

| Circuit Interconnects           | 3 |

| Applications Assistance Form    | 3 |

## **HIGH-SPEED LOGIC**

High speed logic is used whenever improved system performance would increase a product's market value. For a given system design, high–speed logic is the most direct way to improve system performance and Emitter–Coupled Logic (ECL) is one of today's fastest forms of digital logic. Emitter–coupled logic offers both the logic speed and logic features to meet the market demands for higher performance systems.

#### **MECL PRODUCTS**

Motorola, now ON Semiconductor, introduced the original monolithic emitter–coupled logic family with MECL I (1962) and followed this with MECL II (1966). These two families are now obsolete and have given way to the MECL III (MC1600 series), MECL 10K, PLL (MC12000 series) and the new MECL 10H families.

Chronologically the third family introduced, MECL III (1968) is a higher power, higher speed logic. Typical 1 ns edge speeds and propagation delays along with greater than 500 MHz flip—flop toggle rates, make MECL III useful for high—speed test and communications equipment. Also, this family is used in the high—speed sections and critical timing delays of larger systems. For more general purpose applications, however, trends in large high—speed systems showed the need for an easy—to—use logic family with propagation delays on the order of 2 ns. To match this requirement, the MECL 10,000 Series was introduced in 1971.

An important feature of MECL 10K is its compatibility with MECL III to facilitate using both families in the same system. A second important feature is its significant power economy – MECL 10K gates use less than one–half the power of MECL III.

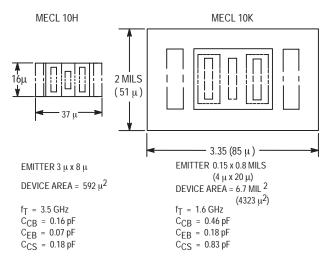

ON Semiconductor introduced the MECL 10H product family in 1981. This latest MECL family features 100% improvements in propagation delay and clock speeds while maintaining power supply currents equal to MECL 10K. MECL 10H is voltage compensated allowing guaranteed dc and switching parameters over a ±5% power supply range. Noise margins have been improved by 75% over the MECL 10K series.

Compatibility with MECL 10K and MECL III is a key element in allowing users to enhance existing systems by

increasing the speed in critical timing areas. Also, many MECL 10H devices are pin out/functional duplications of the MECL 10K series devices. The emphasis of this family will be placed on more powerful logic functions having more complexity and greater performance. With 1.0 ns propagation delays and 25 mW per gate, MECL 10H is one of the best speed–power families of any ECL logic family available today.

#### MECL at +5V (PECL - Positive ECL)

Any single supply ECL device is also a PECL device, making the PECL portfolio as large as the existing ECL one. (Note: The dual supply translator devices cannot operate at +5V and ground and cannot be considered PECL devices.) ECL devices in the PECL mode, must have the input/output DC specifications adjusted for proper operation. ECL levels (DC) are referenced from the  $V_{CC}$  level. To calculate the PECL DC specifications, ECL levels are added to the new  $V_{CC}$ .

#### **EXAMPLE:**

PECL V<sub>OH</sub>=New V<sub>CC</sub>+ECL V<sub>OH</sub>, 5.0V+(-0.81V)=4.190V and is the max V<sub>OH</sub> level at  $25^{\circ}$ C for a PECL device. Follow the same procedure to calculate all input/output DC specifications for a device used in a PECL mode. The V<sub>TT</sub> supply used to sink the parallel termination currents is also referenced from the V<sub>CC</sub> supply and is V<sub>CC</sub>-2.0V. The PECL V<sub>TT</sub> supply = +5V-2V=+3.0V and should track the V<sub>CC</sub> supply one-to-one for specified operation.

Since ECL is referenced from the  $V_{CC}$  rail, any noise on the  $V_{CC}$  supply will be reflected on the output waveshape at a one–to–one ratio. Therefore, noise should be kept as low as possible for best operation. Devices in a PECL system cannot have  $V_{CC}$  vary more than 5% to assure proper AC operation. See ON Semiconductor Application Note AN1406/D "Designing With PECL (ECL at +5.0V)" for more details.

AC performance in the PECL mode is equal to the AC performance in the ECL mode, if the pitfalls set forth in Application Note (AN1406/D) are avoided.

#### MECL FAMILY COMPARISONS

|                           |             | MECL 10K      |               |

|---------------------------|-------------|---------------|---------------|

| Feature                   | MECL 10H    | 10,100 Series | 10,200 Series |

| Gate Propagation Delay    | 1.0 ns      | 2.0 ns        | 1.5 ns        |

| 2. Output Edge Speed*     | 1.0 ns      | 3.5 ns        | 2.5 ns        |

| 3. Flip-Flop Toggle Speed | 250 MHz min | 125 MHz min   | 200 MHz min   |

| 4. Gate Power             | 25 mW       | 25 mW         | 25 mW         |

| 5. Speed Power Product    | 25 pJ       | 50 pJ         | 37 pJ         |

<sup>\*</sup>Output edge speed: MECL 10K/10H measured 20% to 80%.

Figure 1 - GENERAL CHARACTERISTICS

| Ambient<br>Temperature Range | MECL 10H        | MECL 10K                         |

|------------------------------|-----------------|----------------------------------|

| 0° to 75°C                   | MC10H100 Series |                                  |

| −30°C to +85°C               |                 | MC10100 Series<br>MC10200 Series |

Figure 2 - OPERATING TEMPERATURE RANGE

#### **MECL IN PERSPECTIVE**

In evaluating any logic line, speed and power requirements are the obvious primary considerations. Figure 1 and Figure 2 provide the basic parameters of the MECL 10H, MECL 10K, and MECL III families. But these provide only the start of any comparative analysis, as there are a number of other important features that make MECL highly desirable for system implementation. Among these:

**Complementary Outputs** cause a function and its complement to appear simultaneously at the device outputs, without the use of external inverters. It reduces package count by eliminating the need for associated invert functions and, at the same time, cuts system power requirements and reduces timing differential problems arising from the time delays introduced by inverters.

**High Input Impedance and Low Output Impedance** permit large fan out and versatile drive characteristics.

**Insignificant Power Supply Noise Generation,** due to differential amplifier design which eliminates current spikes even during signal transition period.

**Nearly Constant Power Supply Current Drain** simplifies power—supply design and reduces costs.

**Low Cross-Talk** due to low-current switching in signal path and small (typically 850 mV) voltage swing, and to relatively long rise and fall times.

**Wide Variety of Functions,** including complex functions facilitated by low power dissipation (particularly in MECL 10H and MECL 10K series). A basic MECL 10K gate consumes less than 8 mW in on–chip power in some complex functions.

**Wide Performance Flexibility** due to differential amplifier design which permits MECL circuits to be used as linear as well as digital circuits.

**Transmission Line Drive Capability** is afforded by the open emitter outputs of MECL devices. No "Line Drivers" are listed in MECL families, because *every* device is a line driver

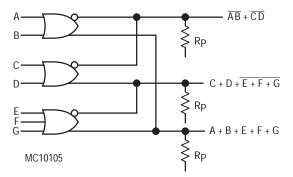

**Wire–ORing** reduces the number of logic devices required in a design by producing additional OR gate functions with only an interconnection.

**Twisted Pair Drive Capability** permits MECL circuits to drive twisted—pair transmission lines as long as 1000 feet.

**Wire–Wrap Capability** is possible with the MECL 10K family because of the slow rise and fall time characteristic of the circuits.

**Open Emitter–Follower Outputs** are used for MECL outputs to simplify signal line drive. The outputs match any line impedance and the absence of internal pulldown resistors saves power.

Input Pulldown Resistors of approximately 50  $k\Omega$  permit unused inputs to remain unconnected for easier circuit board layout.

#### **MECL APPLICATIONS**

ON Semiconductor's MECL product lines are designed for a wide range of systems needs. Within the computer market, MECL 10K is used in systems ranging from special purpose peripheral controllers to large mainframe computers. Big growth areas in this market include disk and communication channel controllers for larger systems and high performance minicomputers.

The industrial market primarily uses MECL for high performance test systems such as IC or PC board testers. However, the high bandwidths of MECL 10H and MECL 10K are required for many frequency synthesizer systems using high speed phase lock loop networks. MECL has

continued to grow in the industrial market through complex medical electronic products and high performance process control systems.

# BASIC CONSIDERATIONS FOR HIGH-SPEED LOGIC DESIGN

High–speed operation involves only four considerations that differ significantly from operation at low and medium speeds:

- 1. Time delays through interconnect wiring, which may have been ignored in medium–speed systems, become highly important at state–of–the–art speeds.

- 2. The possibility of distorted waveforms due to reflections on signal lines increases with edge speed.

- 3. The possibility of "crosstalk" between adjacent signal leads is proportionately increased in high-speed systems.

- 4. Electrical noise generation and pick-up are more detrimental at higher speeds.

In general, these four characteristics are speed—and frequency—dependent, and are virtually independent of the type of logic employed. The merit of a particular logic family is measured by how well it compensates for these deleterious effects in system applications.

The interconnect—wiring time delays can be reduced only by reducing the length of the interconnecting lines. At logic speeds of two nanoseconds, an equivalent "gate delay" is introduced by every foot of interconnecting wiring. Obviously, for functions interconnected within a single monolithic chip, the time delays of signals travelling from one function to another are insignificant. But for a great

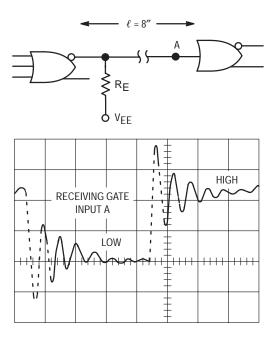

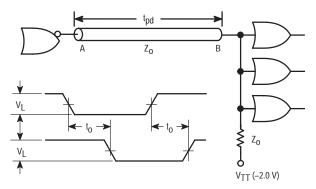

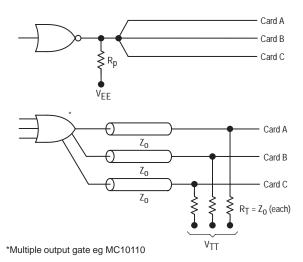

Figure 3 – UNTERMINATED TRANSMISSION LINE (No Ground Plane Used)

many externally interconnected parts, this can soon add up to an appreciable delay time. Hence, the greater the number of functions per chip, the higher the system speed. *MECL circuits, particularly those of the MECL 10K and MECL 10H Series are designed with a propensity toward complex functions to enhance overall system speed.*

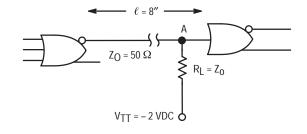

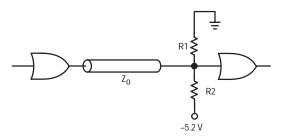

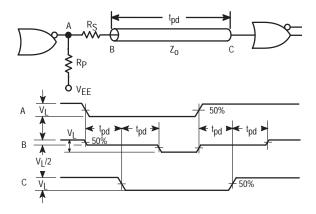

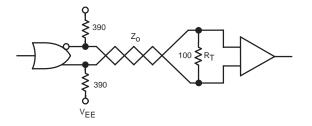

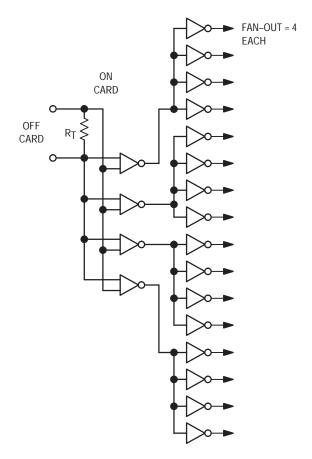

Waveform distortion due to line reflections also becomes troublesome principally at state—of—the—art speeds. At slow and medium speeds, reflections on interconnecting lines are not usually a serious problem. At higher speeds, however, line lengths can approach the wavelength of the signal and improperly terminated lines can result in reflections that will cause false triggering (see Figure 3 and Figure 4). The solution, as in RF technology, is to employ "transmission—line" practices and properly terminate each signal line with its characteristic impedance at the end of its run. The low—impedance, emitter—follower outputs of MECL circuits facilitate transmission—line practices without upsetting the voltage levels of the system.

The increased affinity for crosstalk in high–speed circuits is the result of very steep leading and trailing edges (fast rise and fall times) of the high–speed signal. These steep wavefronts are rich in harmonics that couple readily to adjacent circuits. In the design of MECL 10K and MECL 10H, the rise and fall times have been deliberately slowed. This reduces the affinity for crosstalk without compromising other important performance parameters.

From the above, it is evident that the MECL logic line is not simply capable of operating at high speed, but has been specifically designed to reduce the problems that are normally associated with high–speed operation.

Figure 4 – PROPERLY TERMINATED TRANSMISSION LINE (Ground Plane Added)

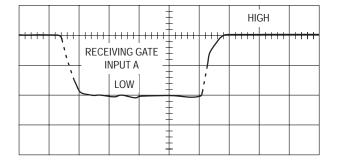

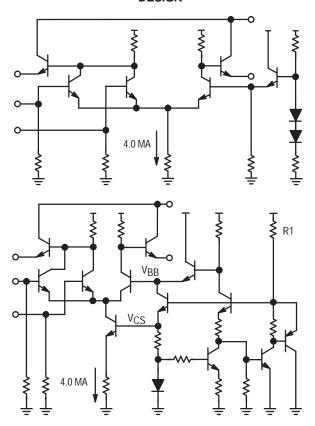

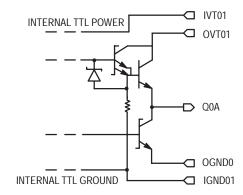

Figure 5 - MECL 10K GATE STRUCTURE AND SWITCHING BEHAVIOR

#### **CIRCUIT DESCRIPTION**

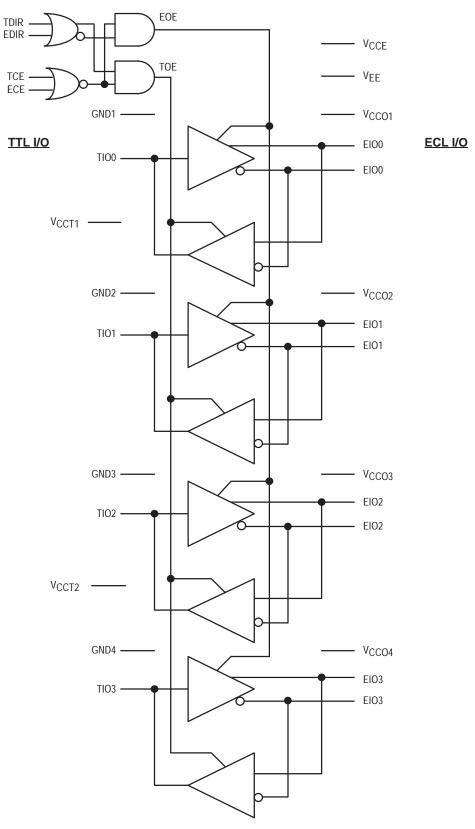

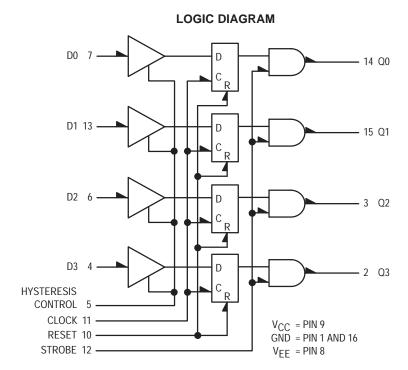

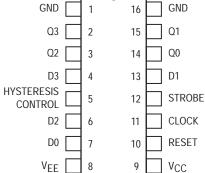

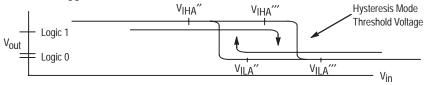

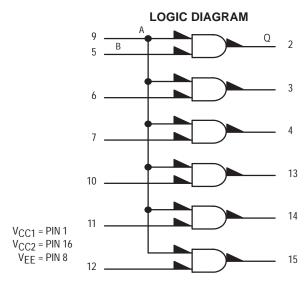

The typical MECL 10K circuit, Figure 5, consists of a differential-amplifier input circuit, a temperature and voltage compensated bias network, and emitter-follower outputs to restore dc levels and provide buffering for transmission line driving. High fan-out operation is possible because of the high input impedance of the differential amplifier input and the low output impedance of the emitter follower outputs. Power-supply noise is virtually eliminated by the nearly constant current drain of the differential amplifier, even during the transition period. Basic gate design provides for simultaneous output of both the OR function and its complement, the NOR function. The design of the MECL 10H gate is unchanged, with two exceptions. The bias network has been replaced with a voltage regulator, and the differential amplifier source resistor has been replaced with a constant current source. (See section 2 for additional MECL 10H information.)

**Power–Supply Connections** – Any of the power supply levels,  $V_{TT}$ ,  $V_{CC}$ , or  $V_{EE}$  may be used as ground; however, the use of the  $V_{CC}$  node as ground results in best noise immunity. In such a case:  $V_{CC} = 0$ ,  $V_{TT} = -2.0$  V,  $V_{EE} = -5.2$  V.

**System Logic Specifications** – The output logic swing of 0.85 V, as shown by the typical transfer characteristics curve, varies from a LOW state of  $V_{OL} = -1.75$  V to a HIGH state of  $V_{OH} = -0.9$  V with respect to ground.

Positive logic is used when reference is made to logical "0's" or "1's." Then

"0" =

$$-1.75 \text{ V} = \text{LOW}$$

typical "1" =  $-0.9 \text{ V} = \text{HIGH}$

Circuit Operation – Beginning with all logic inputs LOW (nominal –1.75 V), assume that Q1 through Q4 are cut off because their P–N base–emitter junctions are not conducting, and the forward–biased Q5 is conducting. Under these conditions, with the base of Q5 held at –1.29 V by the VBB network, its emitter will be one diode drop (0.8 V) more negative than its base, or –2.09 V. (The 0.8 V differential is a characteristic of this P–N junction.) The base–to–emitter differential across Q1 – Q4 is then the difference between the common emitter voltage (–2.09 V) and the LOW logic level (–1.75 V) or 0.34 V. This is less than the threshold voltage of Q1 through Q4 so that these transistors will remain cut off.

When any one (or all) of the logic inputs are shifted upward from the -1.75 V LOW state to the -0.9 V HIGH state, the base voltage of that transistor increases beyond the threshold point and the transistor turns on. When this happens, the voltage at the common–emitter point rises from -2.09 V to -1.7 (one diode drop below the -0.9 V base voltage of the input transistor), and since the base voltage of the fixed–bias transistor (Q5) is held at -1.29 V, the base–emitter voltage Q5 cannot sustain conduction. Hence, this transistor is cut off.

This action is reversible, so that when the input signal(s) return to the LOW state, Q1 – Q4 are again turned off and Q5 again becomes forward biased. The collector voltages resulting from the switching action of Q1 – Q4 and Q5 are transferred through the output emitter–follower to the output terminal. Note that the differential action of the switching transistors (one section being off when the other is on) furnishes simultaneous complementary signals at the output. This action also maintains constant power supply current drain.

#### **DEFINITIONS OF LETTER SYMBOLS AND ABBREVIATIONS**

| Current:                           |                                                                                                                            |                  |                                                                                                                                                                                      |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICC                                | Total power supply current drawn from the positive supply by a MECL unit under test.                                       | $V_{CB}$         | Collector–to–base voltage drop of a transistor at specified collector and base currents.                                                                                             |

| ICBO                               | Leakage current from input transistor on MECL devices without pulldown resistors when test voltage is applied.             | VCC              | General term for the most positive power supply voltage to a MECL device (usually ground, except for translator and interface circuits).                                             |

| ICCH                               | Current drain from V <sub>CC</sub> power supply with all inputs at logic HIGH level.                                       | VCC1             | Most positive power supply voltage (output devices). (Usually ground for MECL devices.)                                                                                              |

| ICCL                               | Current drain from VCC power supply with all inputs at logic LOW level.                                                    | VCC2             | Most positive power supply voltage (current switches and bias driver). (Usually ground for                                                                                           |

| ΙΕ                                 | Total power supply current drawn from a MECL test unit by the negative power supply.                                       | VCMR             | MECL devices.)  The CMR range is referenced to the most                                                                                                                              |

| lF                                 | Forward diode current drawn from an input of a saturated logic–to–MECL translator when that input is at 0.4V.              |                  | positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the specified range and the peak-to-peak voltage lies between Vppmin and |

| l <sub>in</sub>                    | Current into the input of the test unit when a maximum logic HIGH (VIH max) is applied at that input.                      |                  | 1V. The lower end of the CMR range varies 1:1 with VEE. The numbers in the spectable assume a nominal VEE = -5.2V. Note for PECL                                                     |

| INH                                | HIGH level input current into a node with a specified HIGH level (V <sub>IH</sub> max) logic voltage                       |                  | operation, the V <sub>CMR</sub> (min) will be fixed at 5.0V –  V <sub>CMR</sub> (min) .                                                                                              |

|                                    | applied to that node. (Same as I <sub>In</sub> for positive logic.)                                                        | VEE              | Most negative power supply voltage for a circuit (usually –5.2 V for MECL devices).                                                                                                  |

| INL                                | LOW level input current, into a node with a specified LOW level (V <sub>IL min</sub> ) logic voltage applied to that node. | VF               | Input voltage for measuring I <sub>F</sub> on TTL interface circuits.                                                                                                                |

| IL                                 | Load current that is drawn from a MECL circuit                                                                             | VIH              | Input logic HIGH voltage level (nominal value).                                                                                                                                      |

|                                    | output when measuring the output HIGH level voltage.                                                                       | VIH max          | Maximum HIGH level input voltage: The most positive (least negative) value of high-level input voltage, for which operation of the logic                                             |

| ЮН                                 | HIGH level output current: the current flowing into the output, at a specified HIGH level output                           | VIHA             | element within specification limits is guaranteed. Input logic HIGH threshold voltage level.                                                                                         |

| l <sub>OL</sub>                    | voltage.  LOW level output current: the current flowing                                                                    | VIHA min         | Minimum input logic HIGH level (threshold)                                                                                                                                           |

| .OL                                | into the output, at a specified LOW level output voltage.                                                                  | VIH min          | voltage for which performance is specified.  Minimum HIGH level input voltage: The least                                                                                             |

| los                                | Output short circuit current.                                                                                              |                  | positive (most negative) value of HIGH level                                                                                                                                         |

| l <sub>out</sub>                   | Output current (from a device or circuit, under such conditions mentioned in context).                                     |                  | input voltage for which operation of the logic element within specification limits is guaranteed.                                                                                    |

| IOZL                               | Output off current LOW – The current flowing out                                                                           | VIL              | Input logic LOW voltage level (nominal value).                                                                                                                                       |

| 022                                | of a disabled 3-state output with a specified LOW output voltage applied.                                                  | VIL max          | Maximum LOW level input voltage: The most positive (least negative) value of LOW level input voltage for which operation of the logic                                                |

| lozh                               | Output off current HIGH – The current flowing into a disabled 3–state output with a specified                              | VILA             | element within specification limits is guaranteed.  Input logic LOW threshold voltage level.                                                                                         |

| $I_{R}$                            | HIGH output.  Reverse current drawn from a transistor input of                                                             | VILA max         | Maximum input logic LOW level (threshold) voltage for which performance is specified.                                                                                                |

| $I_{R'}$                           | a test unit when VEE is applied to that input.  Reverse current leakage into an input of a                                 | VIL min          | Minimum LOW level input voltage: The least                                                                                                                                           |

| 'IX                                | saturated logic MECL/PECL translator when that input is at V <sub>CC</sub> .                                               |                  | positive (most negative) value of LOW level input voltage for which operation of the logic element within specification limits is guaranteed.                                        |

| ISC                                | Short-circuit current drawn from a translator                                                                              | Vin              | Input voltage (to a circuit or device).                                                                                                                                              |

|                                    | saturating output when that output is at ground potential.                                                                 | V <sub>max</sub> | Maximum (most positive) supply voltage, permitted under a specified set of conditions.                                                                                               |

| Voltage:                           |                                                                                                                            | Vон              | Output logic HIGH voltage level: The voltage                                                                                                                                         |

| V <sub>BB</sub><br>V <sub>BE</sub> | Reference bias supply voltage.  Base—to—emitter voltage drop of a transistor at                                            | 011              | level at an output terminal for a specified output current, with the specified conditions applied to establish a HIGH level at the output.                                           |

|                                    | specified collector and base currents.                                                                                     | t <sub>AA</sub>  | Address Access Time                                                                                                                                                                  |

|                                    |                                                                                                                            | -7/7             |                                                                                                                                                                                      |

#### Voltage (cont.):

VOHA Output logic HIGH threshold voltage level.

VOHA min Minimum output HIGH threshold voltage level

for which performance is specified.

VOH max Maximum output HIGH or high-level voltage for

given inputs.

VOH min Minimum output HIGH or high-level voltage for

given inputs.

VOL Output logic LOW voltage level: The voltage

level at the output terminal for a specified output current, with the specified conditions applied to

establish a LOW level at the output.

VOLA Output logic LOW threshold voltage level.

VOLA max Maximum output LOW threshold voltage level

for which performance is specified.

VOL max Maximum output LOW level voltage for given

inputs.

VOL min Minimum output LOW level voltage for given

inputs.

V<sub>TT</sub> Line load-resistor terminating voltage for

outputs from a MECL device.

#### **Time Parameters:**

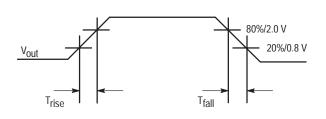

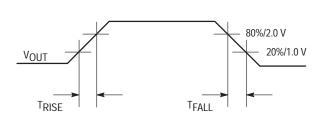

t+ Waveform rise time (LOW to HIGH), 10% to

90%, or 20% to 80%, as specified.

t- Waveform fall time (HIGH to LOW), 90% to 10%,

or 80% to 20%, as specified.

t<sub>r</sub> Same as t+

tf Same as t-

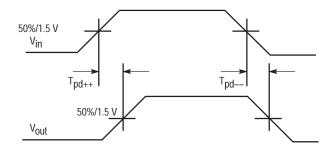

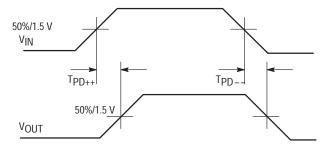

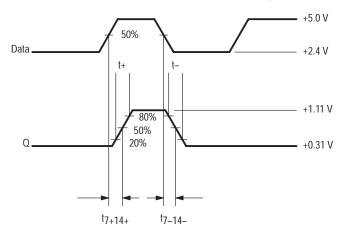

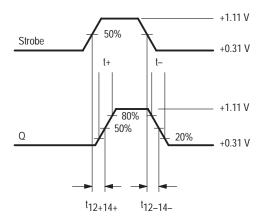

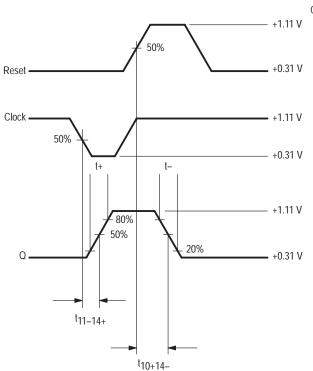

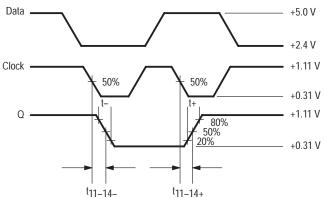

t+- Propagation Delay, see Figure 12 on page 24.

t-+ Propagation Delay, see Figure 12 on page 24.

tpd Propagation delay, input to output from the 50%

point of the input waveform at pin x (falling edge

$t_{X\pm V\pm}$  noted by – or rising edge noted by +) to the 50%

point of the output waveform at pin y (falling edge noted by – or rising edge noted by +). (Cf

Figure 12 on page 24.)

t<sub>X+</sub> Output waveform rise time as measured from

10% to 90% or 20% to 80% points on waveform (whichever is specified) at pin x with input

conditions as specified.

t<sub>X-</sub> Output waveform fall time as measured from

90% to 10% or 80% to 20% points on waveform

(whichever is specified) at pin x, with input

conditions as specified.

f<sub>Tog</sub> Toggle frequency of a flip–flop or counter device.

f<sub>Shift</sub> Shift rate for a shift register.

#### Temperature:

T<sub>stg</sub> Maximum temperature at which device may be

stored without damage or performance

degradation.

T<sub>J</sub> Junction (or die) temperature of an integrated

circuit device.

T<sub>A</sub> Ambient (environment) temperature existing in

the immediate vicinity of an integrated circuit

device package.

θ<sub>J</sub>A Thermal resistance of an IC package, junction to

ambient.

θJC Thermal resistance of an IC package, junction to

case.

Ifpm Linear feet per minute.

$\theta_{CA}$  Thermal resistance of an IC package, case to

ambient.

#### Miscellaneous:

eg Signal generator inputs to a test circuit.

TPin Test point at input of unit under test.

TP<sub>OUt</sub> Test point at output of unit under test.

D.U.T. Device under test.

Cin Input capacitance.

Cout Output capacitance.

Z<sub>out</sub> Output impedance.

Pn The total dc power applied to a device, not

including any power delivered from the device to

a load.

R<sub>L</sub> Load Resistance.

RT Terminating (load) resistor.

R<sub>D</sub> An input pull-down resistor (i.e., connected to

the most negative voltage).

P.U.T. Pin under test.

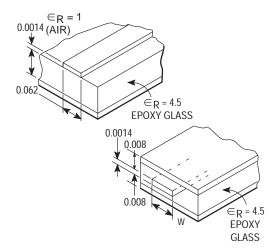

## **MECL Logic Surface Mount**

#### WHY SURFACE MOUNT?

Surface Mount Technology is now being utilized to offer answers to many problems that have been created in the use of insertion technology.

Limitations have been reached with insertion packages and PC board technology. Surface Mount Technology offers the opportunity to continue to advance the State-of-the-Art designs that cannot be accomplished with Insertion Technology.

Surface Mount Packages allow more optimum device performance with the smaller Surface Mount configuration. Internal lead lengths, parasitic capacitance and inductance that placed limitations on chip performance have been reduced.

The lower profile of Surface Mount Packages allows more boards to be utilized in a given amount of space. They are stacked closer together and utilize less total volume than insertion populated PC boards.

Printed circuit costs are lowered with the reduction of the number of board layers required. The elimination or reduction of the number of plated through holes in the board, contribute significantly to lower PC board prices.

Surface Mount assembly does not require the preparation of components that are common on insertion technology lines. Surface Mount components are sent directly to the assembly line, eliminating an intermediate step.

Automatic placement equipment is available that can place Surface Mount components at the rate of a few thousand per hour to hundreds of thousands of components per hour.

Surface Mount Technology is cost effective, allowing the manufacturer the opportunity to produce smaller units and offer increased functions with the same size product.

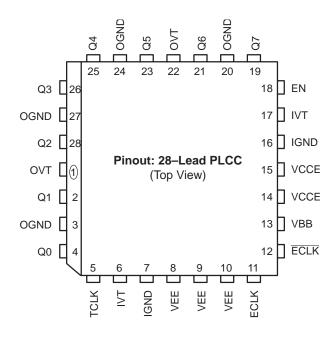

#### MECL AVAILABILITY IN SURFACE MOUNT

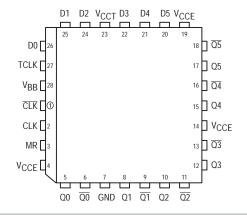

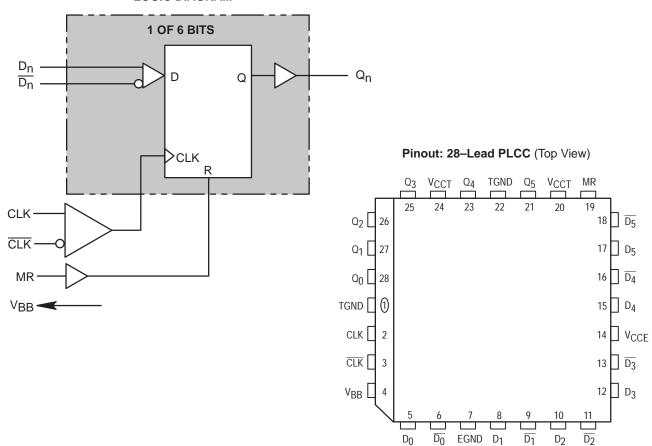

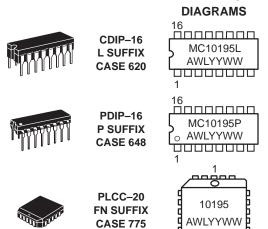

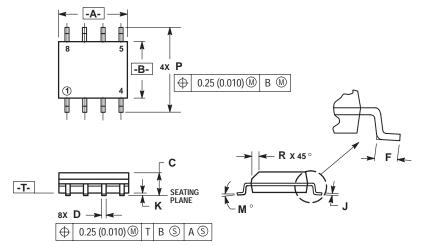

ON Semiconductor is now offering MECL 10K and MECL 10H in the PLCC (Plastic Leaded Chip Carrier) packages.

MECL in PLCC may be ordered in conventional plastic rails or on Tape and Reel. Refer to the Tape and Reel section for ordering details.

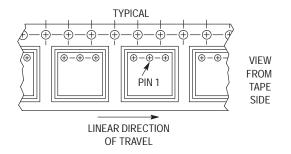

#### **TAPE AND REEL**

ON Semiconductor has now added the convenience of Tape and Reel packaging for our growing family of standard

Integrated Circuit products. The packaging fully conforms to the latest EIA RS-481A specification. The antistatic embossed tape provides a secure cavity sealed with a peel-back cover tape.

#### **GENERAL INFORMATION**

• Reel Size 13 inch (330 mm) Suffix: R2

Tape Width 16 mmUnits/Reel 1000

#### **MECHANICAL POLARIZATION**

#### ORDERING INFORMATION

- Minimum Lot Size/Device Type = 3000 Pieces.

- No Partial Reel Counts Available.

- To order devices which are to be delivered in Tape and Reel, add the appropriate suffix to the device number being ordered.

#### **EXAMPLE:**

| ORDERING CODE | SHIPMENT METHOD       |

|---------------|-----------------------|

| MC10101FN     | Magazines (Rails)     |

| MC10101FNR2   | 13 inch Tape and Reel |

| MC10H101FN    | Magazines (Rails)     |

| MC10H101FNR2  | 13 inch Tape and Reel |

| MC12015D      | Magazines (Rails)     |

| MC12015DR2    | 13 inch Tape and Reel |

|               |                       |

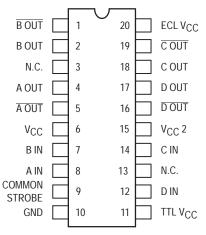

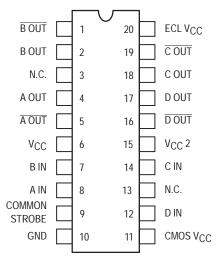

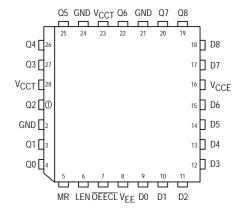

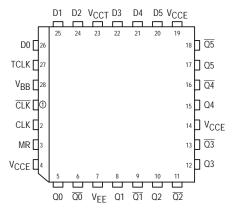

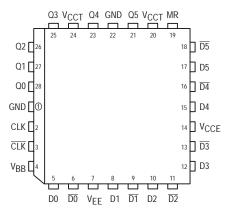

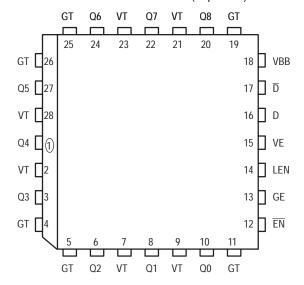

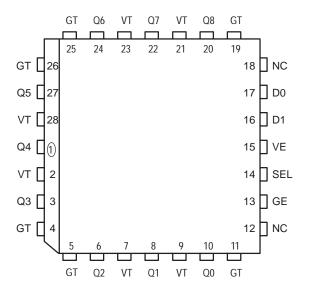

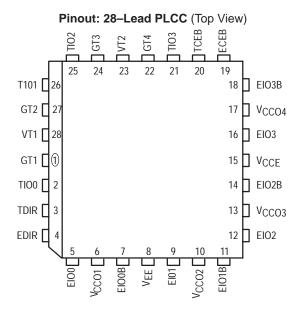

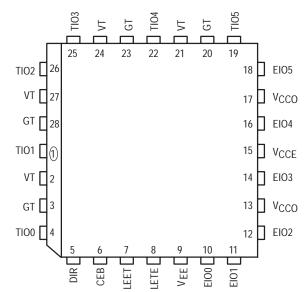

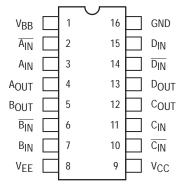

# DUAL-IN-LINE PACKAGE TO PLCC PIN CONVERSION DATA

The following tables give the equivalent I/O pinouts of Dual-In-Line (DIL) packages and Plastic Leaded Chip Carrier (PLCC) packages.

## **Pin Conversion Tables**

#### 8-Pin DIL to 20-Pin PLCC

| 8 PIN DIL   | 1 | 2 | 3 | 4  | 5  | 6  | 7  | 8  |

|-------------|---|---|---|----|----|----|----|----|

| 20 PIN PLCC | 2 | 5 | 7 | 10 | 12 | 15 | 17 | 20 |

#### 14-Pin DIL to 20-Pin PLCC

| 14 PIN DIL  | 1 | 2 | 3 | 4 | 5 | 6 | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |  |

|-------------|---|---|---|---|---|---|----|----|----|----|----|----|----|----|--|

| 20 PIN PLCC | 2 | 3 | 4 | 6 | 8 | 9 | 10 | 12 | 13 | 14 | 16 | 18 | 19 | 20 |  |

#### 16-Pin DIL to 20-Pin PLCC

| 16 PIN DIL  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|-------------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|

| 20 PIN PLCC | 2 | 3 | 4 | 5 | 7 | 8 | 9 | 10 | 12 | 13 | 14 | 15 | 17 | 18 | 19 | 20 |

#### 20-Pin DIL to 20-Pin PLCC

| 20 PIN DIL  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

|-------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|

| 20 PIN PLCC | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

#### 24-Pin DIL to 28-Pin PLCC

| 24 PIN DIL  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |  |

|-------------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--|

| 28 PIN PLCC | 2 | 3 | 4 | 5 | 6 | 7 | 9 | 10 | 11 | 12 | 13 | 14 | 16 | 17 | 18 | 19 | 20 | 21 | 23 | 24 | 25 | 26 | 27 | 28 |  |

#### MECL POSITIVE AND NEGATIVE LOGIC

#### INTRODUCTION

The increasing popularity and use of emitter coupled logic has created a dilemma for some logic designers. Saturated logic families such as TTL have traditionally been designed with the NAND function as the basic logic function, however, the basic ECL logic function is the NOR function (positive logic). Therefore, the designer may either design ECL systems with positive logic using the NOR, or design

with negative logic using the NAND. Which is the more convenient? On the one hand the designer is familiar with positive logic levels and definitions, and on the other hand, he is familiar with implementing systems using NAND functions. Perhaps a presentation of the basic definitions and characteristics of positive and negative logic will clarify the situation and eliminate misunderstanding.

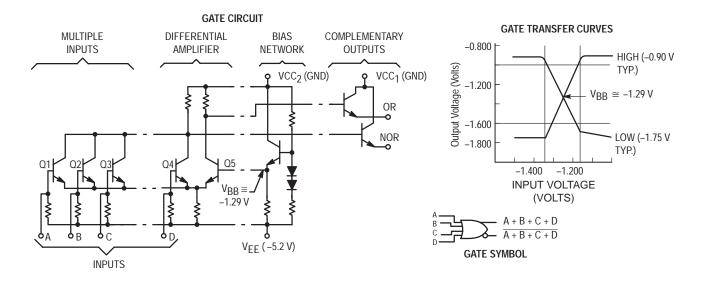

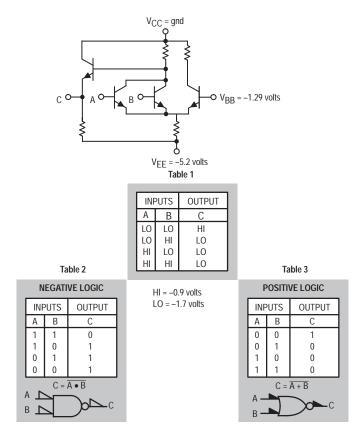

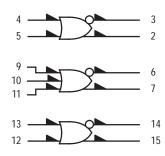

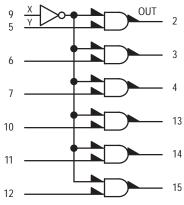

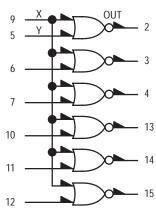

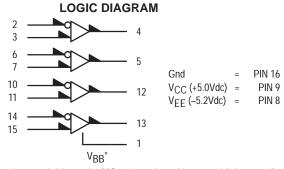

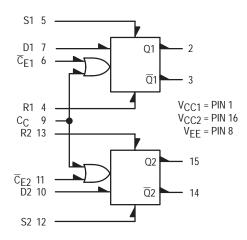

Figure 6 – Basic MECL Gate Circuit and Logic Function In Positive and Negative Nomenclature.

Circuit diagrams external to ON Semiconductor products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this Application Note has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of ON Semiconductor or others.

#### **LOGIC EQUIVALENCIES**

Binary logic must have two states to represent the binary 1 and 0. With ECL the typical states are a high level of -0.9 volts and a low level of -1.7 volts. Two choices are possible then to represent the binary 1 and 0. Positive logic defines the 1 or "true" state as the most positive voltage level, whereas negative logic defines the most negative voltage level as the 1 or "true" state. Because of the difference in definition of states, the basic ECL gate is a NOR function in positive logic and is a NAND function in negative logic.

Figure 6 more clearly shows the above comparison of functions. Table 1 lists the output voltage level as a function of input voltage levels of the MECL gate circuit shown. Table 2 translates the voltage levels into the appropriate negative logic levels which show the function to be  $C = \overline{A \bullet B}$ ; that is, the circuit performs the NAND function.

Table 3 translates the equivalent positive logic function into  $C = \overline{A + B}$ , the NOR function.

Similar comparisons could be made for other positive logic functions. As an example, the positive OR function translates to the negative AND function. Figure 7 shows a comparison of several common logic functions.

Any function available in a logic family may be expressed in terms of positive or negative logic, bearing in mind the definition of logic levels. The choice of logic definition, as previously stated, is dependent on the designer. ON Semiconductor provides both positive and negative logic symbols on data sheets for the popular MECL 10,000 logic series.

|                      |                      |                |                | POSITIV        | E LOGIC              |                      |                      |

|----------------------|----------------------|----------------|----------------|----------------|----------------------|----------------------|----------------------|

| INP                  | UTS                  |                |                |                |                      |                      |                      |

| А                    | В                    | AND            | OR             | NAND           | NOR                  | EXOR                 | EXNOR                |

| LO<br>LO<br>HI<br>HI | LO<br>HI<br>LO<br>HI | LO<br>LO<br>HI | LO<br>HI<br>HI | HI<br>HI<br>LO | HI<br>LO<br>LO<br>LO | LO<br>HI<br>HI<br>LO | HI<br>LO<br>LO<br>HI |

| А                    | В                    | OR             | AND            | NOR            | NAND                 | EXNOR                | EXOR                 |

| INP                  | UTS                  |                |                | 400            | 44                   |                      |                      |

|                      |                      |                |                | NEGATIV        | E LOGIC              |                      |                      |

Figure 7 - Comparative Positive and Negative Logic Functions.

#### **SUMMARY**

Conversion from one logic form to another or the use of a particular logic form need not be a complicated process. If the designer uses the logic form with which he is familiar and bears in mind the previously mentioned definition of levels, problems arising from definition of logic functions should be minimized.

#### **REFERENCE**

Y. Chu, Digital Computer Design Fundamentals New York, McGraw–Hill, 1962

## **TECHNICAL DATA**

#### **GENERAL CHARACTERISTICS AND SPECIFICATIONS**

(See pages 15 through 16 for definitions of symbols and abbreviations.)

In subsequent sections of this Data Book, the important MECL parameters are identified and characterized, and complete data provided for each of the functions. To make this data as useful as possible, and to avoid a great deal of repetition, the data that is common to all functional blocks in a line is not repeated on each individual sheet. Rather, these common characteristics, as well as the application information that applies to each family, are discussed in this section.

In general, the common characteristics of major importance are:

**Maximum Ratings,** including both dc and ac characteristics and temperature limits;

**Transfer Characteristics,** which define logic levels and switching thresholds;

**DC Parameters,** such as output levels, threshold levels, and forcing functions.

**AC Parameters,** such as propagation delays, rise and fall times and other time dependent characteristics.

In addition, this section will discuss general layout and design guides that will help the designer in building and testing systems with MECL circuits.

#### LETTER SYMBOLS AND ABBREVIATIONS

Throughout this section, and in the subsequent data sheets, letter symbols and abbreviations will be used in discussing electrical characteristics and specifications. The symbols used in this book, and their definitions, are listed on the preceding pages.

#### **MAXIMUM RATINGS**

The limit parameters beyond which the life of the devices may be impaired are given in Table 4. In addition, Table 5 provides certain limits which, if exceeded, will not damage the devices, but could degrade the performance below that of the guaranteed specifications.

Table 4 - LIMITS BEYOND WHICH DEVICE LIFE MAY BE IMPAIRED

| Characteristic                       | Symbol           | Unit | MECL 10H    | MECL 10K    |

|--------------------------------------|------------------|------|-------------|-------------|

| Power Supply                         | VEE              | Vdc  | -8.0 to 0   | -8.0 to 0   |

| Input Voltage (V <sub>CC</sub> = 0)  | V <sub>in</sub>  | Vdc  | 0 to VEE    | 0 to VEE    |

| Output Source Current Continuous     | l <sub>out</sub> | mAdc | 50          | 50          |

| Output Source Current Surge          | l <sub>out</sub> | mAdc | 100         | 100         |

| Storage Temperature                  | T <sub>stg</sub> | °C   | -65 to +150 | -65 to +150 |

| Junction Temperature Ceramic Package | TJ               | °C   | 165         | 165         |

| Junction Temperature Plastic Package | TJ               | °C   | 140         | 140         |

NOTES: 1. Maximum  $T_J$  may be exceeded ( $\leq 250^{\circ}$ C) for short periods of time ( $\leq 240$  hours) without significant reduction in device life.

Table 5 - LIMITS BEYOND WHICH PERFORMANCE MAY BE DEGRADED

| Characteristics                        | Symbol         | Unit | MECL 10H         | MECL 10K         |

|----------------------------------------|----------------|------|------------------|------------------|

| Operating Temperature Range Commercial | T <sub>A</sub> | °C   | 0 to +75         | -30 to +85       |

| Supply Voltage (V <sub>CC</sub> = 0)   | VEE            | Vdc  | -4.94 to -5.46   | -4.68 to -5.72   |

| Output Drive Commercial                | -              | Ω    | 50 Ω to –2.0 Vdc | 50 Ω to –2.0 Vdc |

NOTES: 1. With airflow ≥ 500 lfpm.

- 2. Functionality only. Data sheet limits are specified for –5.2 V  $\pm\,0.010$  V.

- 3. Except MC1648 which has an internal output pulldown resistor.

- 4. Functional and Data sheet limits.

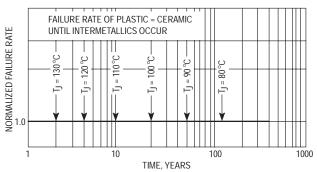

<sup>2.</sup> For long term (≥ 10 yrs.) max T<sub>J</sub> of 110°C required. Max T<sub>J</sub> may be exceeded (≤ 175°C) for short periods of time (≤ 240 hours) without significant reduction in device life.

#### **MECL TRANSFER CURVES and SPECIFICATION TEST POINTS**

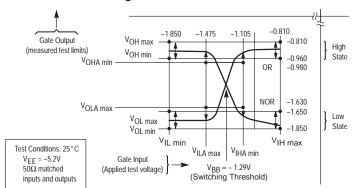

Figure 8 - MECL 10K

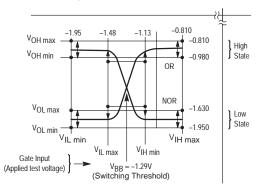

Figure 9 - MECL 10H

#### **MECL TRANSFER CURVES**

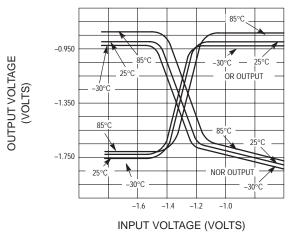

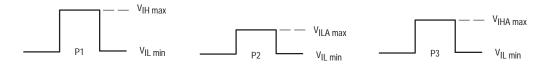

For MECL logic gates, the dual (complementary) outputs must be represented by two transfer curves: one to describe the OR switching action and one to describe the NOR switching action. Typical transfer curves and associated data for the MECL 10K/10H family are shown in Figure 8 and Figure 9, respectively.

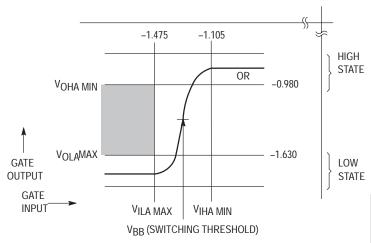

It is not necessary to measure transfer curves at all points of the curves. To guarantee correct operation it is sufficient merely to measure two sets of min/max logic level parameters.

The first set is obtained for 10 K by applying test voltages, V<sub>IL</sub>  $_{\text{min}}$  and V<sub>IH</sub>  $_{\text{max}}$  (sequentially) to the gate inputs, and measuring the OR and NOR output levels to make sure they are between V<sub>OL</sub>  $_{\text{max}}$  and V<sub>OL</sub>  $_{\text{min}}$ , and V<sub>O</sub>  $_{\text{min}}$  specifications.

The second set of logic level parameters relates to the switching thresholds. This set of data is distinguished by an "A" in symbol subscripts. A test voltage, V<sub>ILA max</sub>, is applied to the gate and the NOR and OR outputs are measured to see that they are above the V<sub>OHA min</sub> and below the V<sub>OLA max</sub> levels, respectively. Similar checks are made using the test input voltage V<sub>IHA min</sub>.

The result of these specifications insures that:

- (a) The switching threshold ( $\approx V_{BB}$ ) falls within the darkest rectangle; i.e. switching does not begin outside this rectangle;

- (b) Quiescent logic levels fall in the lightest shaded ranges;

- (c) Guaranteed noise immunity is met.

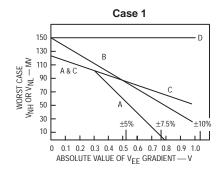

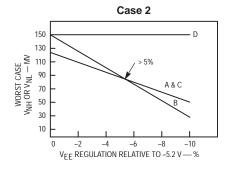

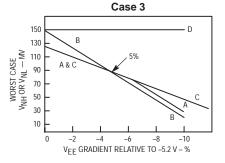

As shown in Figure 10, MECL 10K outputs rise with increasing ambient temperature. All circuits in each family have the same worst–case output level specifications regardless of power dissipation or junction temperature differences to reduce loss of noise margin due to thermal differences.

All of these specifications assume –5.2 V power supply operation. Operation at other power–supply voltages is possible, but will result in further transfer curve changes. Table 6 gives rate of change of output voltages as a function of power supply.

Figure 10 – TYPICAL TRANSFER CHARACTERISTICS AS A FUNCTION OF TEMPERATURE (MECL 10K)

Table 6 - TYPICAL LEVEL CHANGE RATES / 1V

| Voltage                            | MECL 10H | MECL 10K |

|------------------------------------|----------|----------|

| $\Delta V_{OH/}\Delta V_{EE}$      | 0.008    | 0.016    |

| ΔV <sub>OL</sub> /ΔV <sub>EE</sub> | 0.020    | 0.250    |

| $\Delta V_{BB} / \Delta V_{EE}$    | 0.010    | 0.148    |

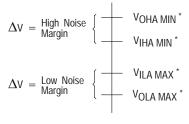

#### **NOISE MARGIN**

"Noise margin" is a measure of logic circuit's resistance to undesired switching. MECL noise margin is defined in terms of the specification points surrounding the switching threshold. The critical parameters of interest here are those designated with the "A" subscript (VOHA min, VOLA max, VIHA min, VILA max) in the transfer characteristic curves. MECL 10H is specified and tested with:

VOHA min = VOH min VOLA max = VOL max VIHA min = VIH min and

$V_{ILA\ max} = V_{IL\ max}$

Guaranteed noise margin (NM) is defined as follows:

NMHIGH LEVEL = VOHA min - VIHA min NMLOW LEVEL = VILA max - VOLA max

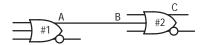

To see how noise margin is computed, assume a MECL gate drives a similar MECL gate, Figure 11.

At a gate input (point B) equal to V<sub>ILA max</sub>, MECL gate #2 can begin to enter the shaded transition region.

This is a "worst case" condition, since the  $V_{OLA\ max}$  specification point guarantees that no device can enter the transition region before an input equal to  $V_{ILA\ max}$  is reached. Clearly then,  $V_{ILA\ max}$  is one critical point for noise margin computation, since it is the edge of the transition region.

To find the other critical voltage, consider the output from MECL gate #1 (point A). What is the most positive value possible for this voltage (considering worst case specifications)? From Figure 11 it can be observed that the VOLA max specification insures that the LOW state OR output from gate #1 can be no greater than VOLA max.

Note that  $V_{OLA\,max}$  is more negative than  $V_{ILA\,max}$ . Thus, with  $V_{OLA\,max}$  at the input to gate #2, the transition region is not yet reached. (The input voltage to gate #2 is still to the left of  $V_{ILA\,max}$  on the transfer curve.)

In order to ever run the chance of switching gate #2, we would need an additional voltage, to move the input from

$V_{OLA\,max}$  to  $V_{ILA\,max}$ . This constitutes the "safety factor" known as noise margin. It can be calculated as the magnitude of the difference between the two specification voltages, or for the MECL 10K levels shown:

Similarly, for the HIGH state:

Analogous results are obtained when considering the "NOR" transfer data.

Note that these noise margins are absolute worst case conditions. The lessor of the two noise margins is that for the HIGH state, 125 mV. This then, constitutes the guaranteed margin against signal undershoot, and power or thermal disturbances.

As shown in the table, typical noise margins are usually better than guaranteed – by about 75 mV. For MECL 10H the "noise margin" is 150 mV for NM low and NM high. (See Section 3 for details.)

Noise margin is a dc specification that can be calculated, since it is defined by specification points tabulated on MECL data sheets. However, by itself, this specification does not give a complete picture regarding the noise immunity of a system built with a particular set of circuits. Overall system noise immunity involves not only noise—margin specifications, but also other circuit—related factors that determine how difficult it is to apply a noise signal of sufficient magnitude and duration to cause the circuit to propagate a false logic state. In general, then, noise immunity involves line impedances, circuit output impedances, and propagation delay in addition to noise—margin specifications. This subject to discussed in greater detail in the MECL System Design Handbook, HB205/D.

Figure 11 - MECL Noise Margin Data

$^*$  VOHA min = VOH min, VOLA max = VOL max, VIHA min = VIH min and VILA max = VIL max for MECL 10H.

#### **Noise Margin Computations**

| Family   | Guaranteed<br>Worst-Case dc<br>Noise Margin<br>(V) | Typical dc<br>Noise Margin<br>(V) |

|----------|----------------------------------------------------|-----------------------------------|

| MECL 10H | 0.150                                              | 0.270                             |

| MECL 10K | 0.125                                              | 0.210                             |

**Specification Points for Determining Noise Margin**

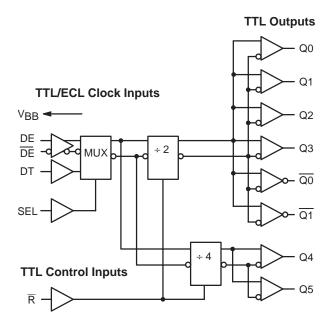

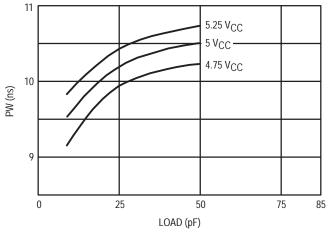

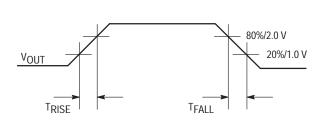

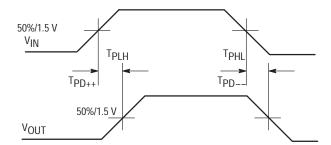

#### **AC OR SWITCHING PARAMETERS**

Time-dependent specifications are those that define the effects of the circuit on a specified input signal, as it travels through the circuit. They include the time delay involved in changing the output level from one logic state to another. In addition, they include the time required for the output of a circuit to respond to the input signal, designated as

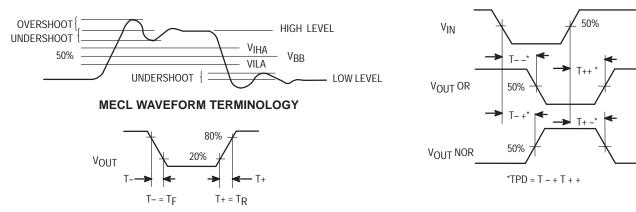

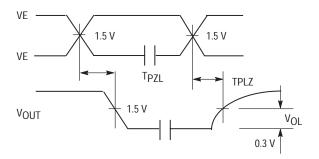

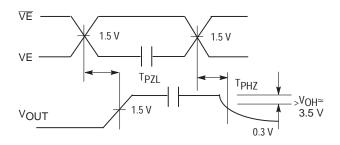

MECL 10K and MECL 10H Rise and Fall Times

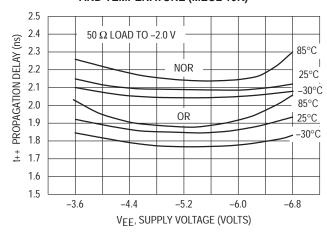

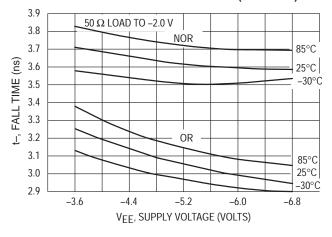

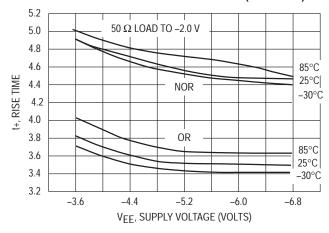

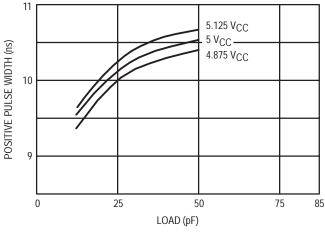

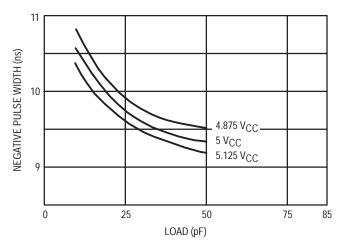

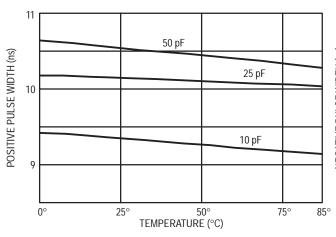

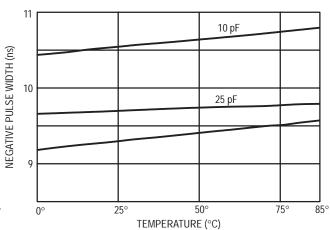

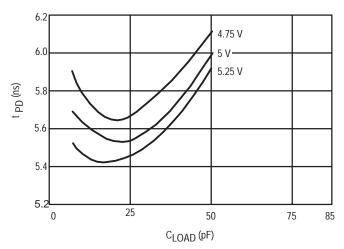

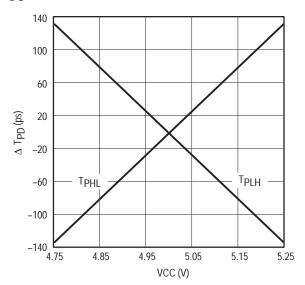

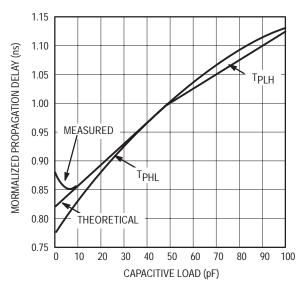

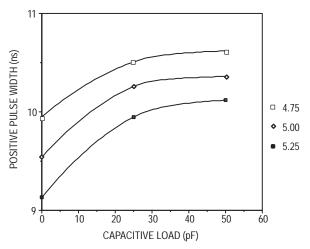

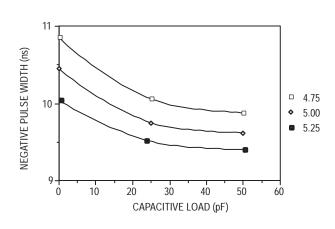

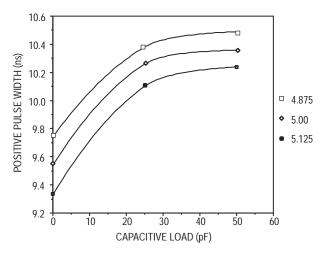

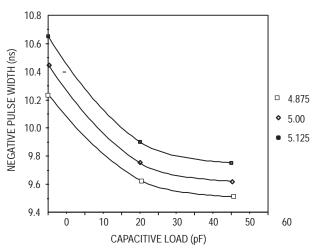

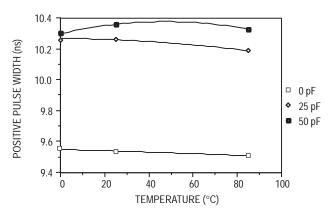

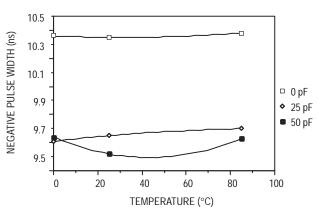

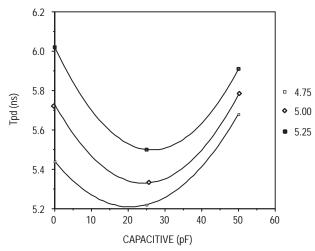

propagation delay, MECL waveform and propagation delay terminologies are depicted in Figure 12. Specific rise, fall, and propagation delay times are given on the data sheet for each specific functional block, but like the transfer characteristics, ac parameters are temperature and voltage dependent. Typical variations for MECL 10K are given in the curves of Figure 13 through Figure 16.

Figure 12 - TYPICAL LOGIC WAVEFORMS

**MECL Propagation Delay**

Figure 13 – TYPICAL PROPAGATION DELAY t- - versus VFF AND TEMPERATURE (MECL 10K)

Figure 14 – TYPICAL PROPAGATION DELAY t+ + versus VEE AND TEMPERATURE (MECL 10K)

Figure 15 – TYPICAL FALL TIME (90% to 10%) versus TEMPERATURE AND SUPPLY VOLTAGE (MECL 10K)

Figure 16 – TYPICAL FALL TIME (10% to 90%) versus TEMPERATURE AND SUPPLY VOLTAGE (MECL 10K)

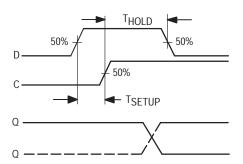

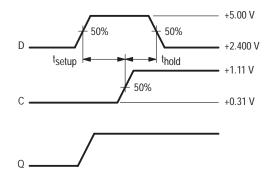

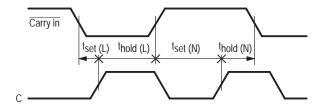

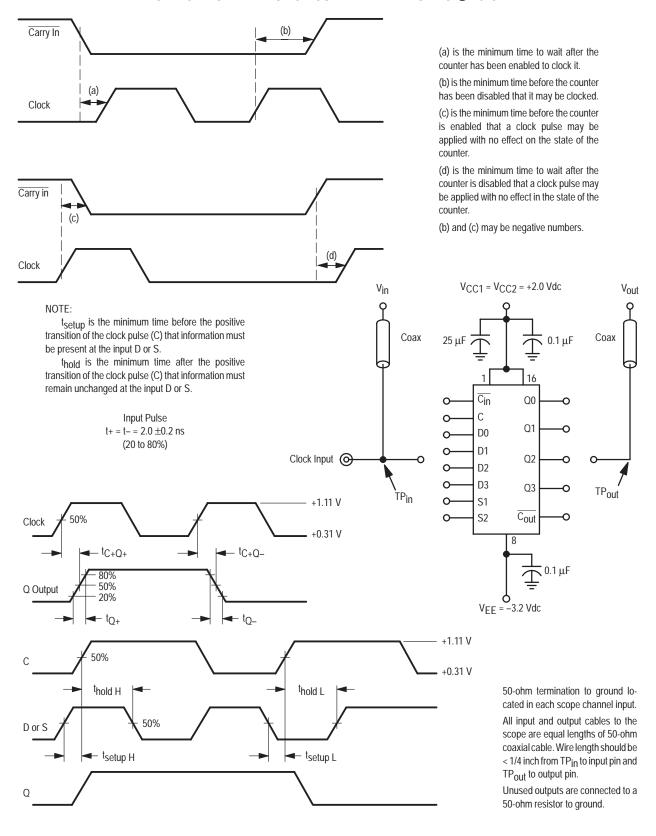

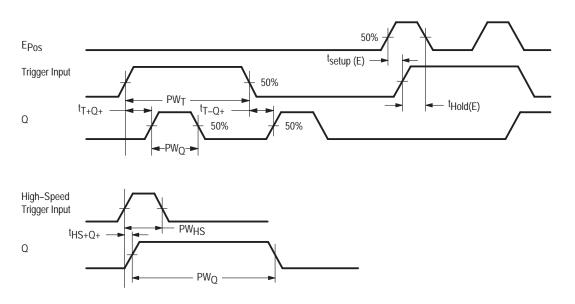

#### **SETUP AND HOLD TIMES**

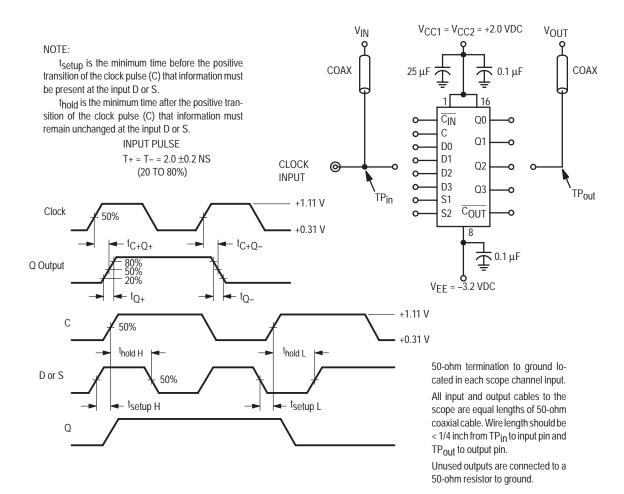

Setup and hold times are two ac parameters which can easily be confused unless clearly defined. For MECL logic devices,  $t_{setup}$  is the minimum time (50% -50%) before the positive transition of the clock pulse (C) that information must be present at the Data input (D) to insure proper operation of the device. The  $t_{hold}$  is defined similarly as the minimum time after the positive transition of the clock pulse (C) that the information must remain unchanged at the Data input (D) to insure proper operation. Setup and hold waveforms for logic devices are shown in Figure 17.

Figure 17 – SETUP AND HOLD WAVEFORMS FOR MECL LOGIC DEVICES

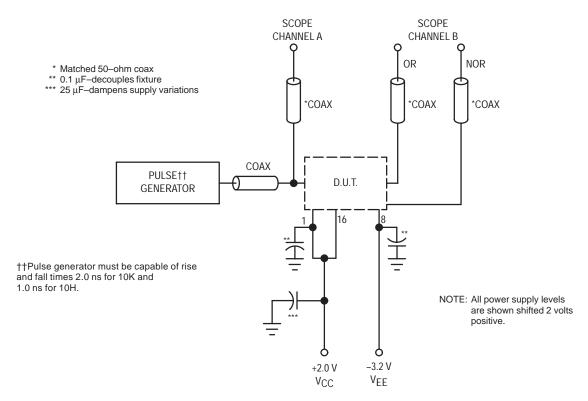

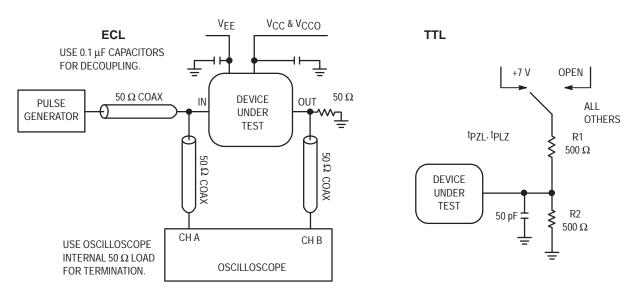

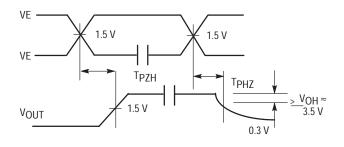

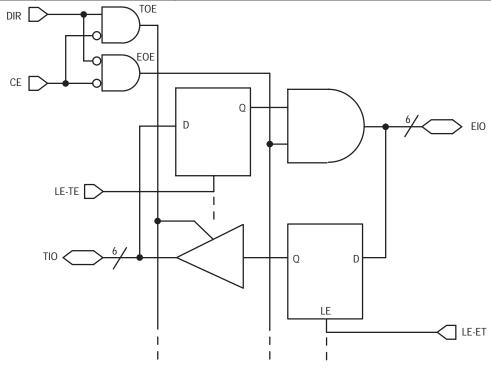

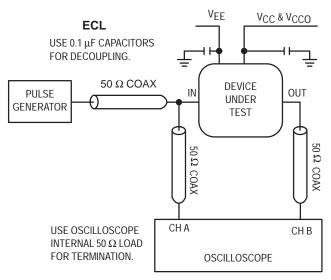

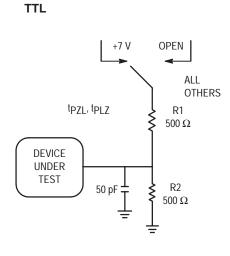

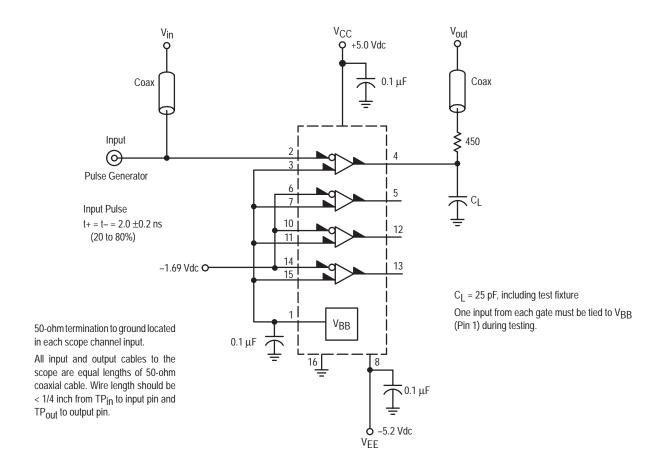

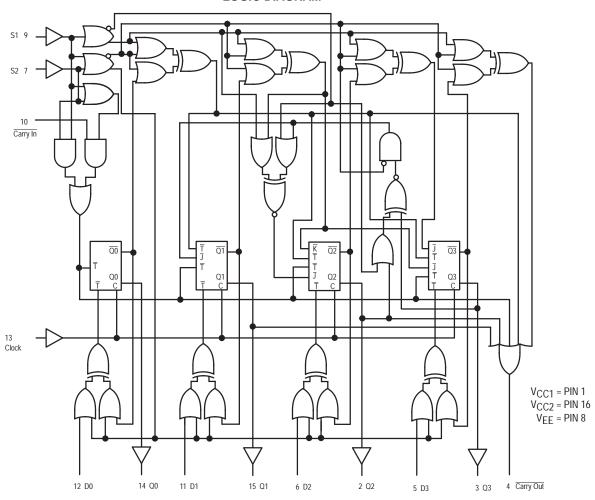

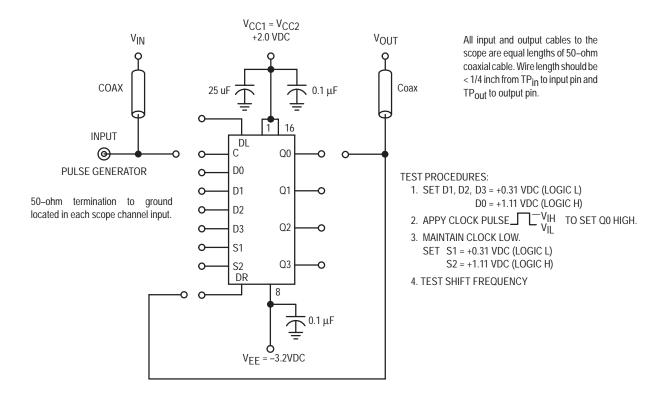

#### **TESTING MECL 10H AND MECL 10K**

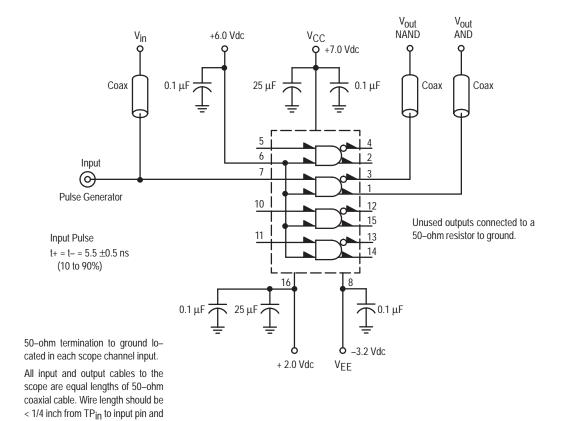

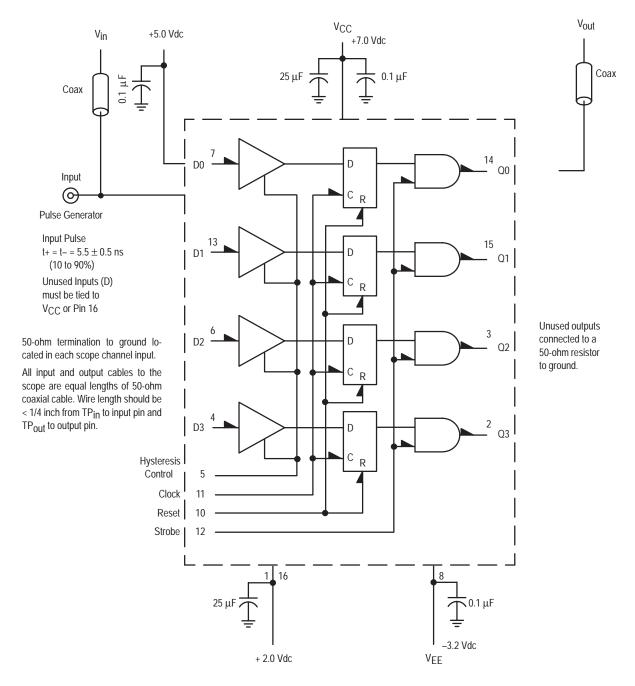

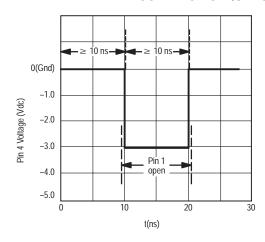

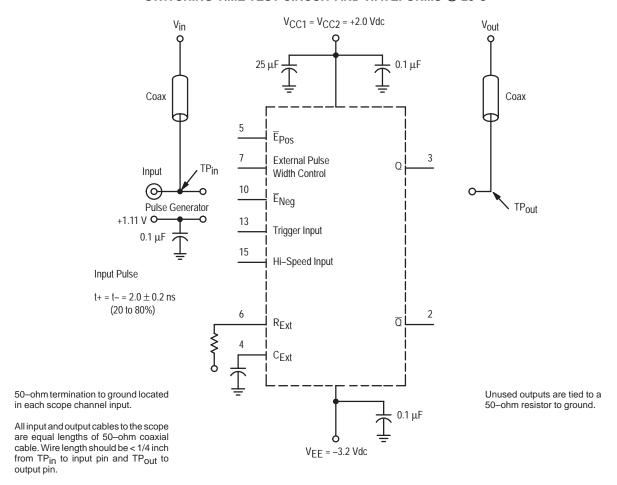

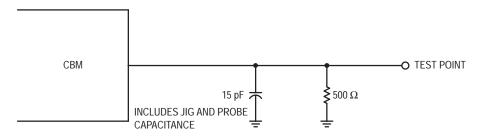

To obtain results correlating with ON Semiconductor circuit specifications certain test techniques must be used. A schematic of a typical gate test circuit is shown in Figure 18. This test circuit is the standard ac test configuration for most MECL devices. (Exceptions are shown with device specification.)

A solid ground plane is used in the test setup, and capacitors bypass V<sub>CC1</sub>, V<sub>CC2</sub>, and V<sub>EE</sub> pins to ground. All power leads and signal leads are kept as short as possible.

The sampling scope interface runs directly to the 50–ohm inputs of Channel A and B via 50–ohm coaxial cable. Equal–length coaxial cables must be used between the test set and the A and B scope inputs. A 50–ohm coax cable such as RG58/U or RG188A/U, is recommended.

Interconnect fittings should be 50–ohm GR, BNC, Sealectro Conhex, or equivalent. Wire length should be  $<\frac{1}{4}$  inch from TP<sub>in</sub> to input pin and TP<sub>out</sub> to output pin.

The pulse generator must be capable of 2.0 ns rise and fall times for MECL 10K and 1.5 ns for MECL 10H and MECL

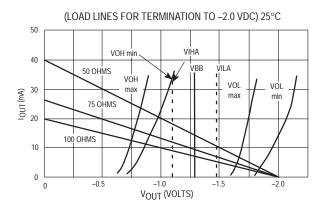

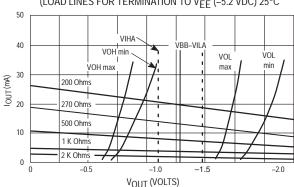

III. In addition, the generator voltage must have an offset to give MECL signal swings of  $\approx \pm 400$  mV about a threshold of  $\approx +0.7$  V when  $V_{CC}=+2.0$  and  $V_{EE}=-3.2$  V for ac testing of logic devices.

The power supplies are shifted +2.0 V, so that the device under test has only one resistor value to load into the precision 50–ohm input impedance of the sampling oscilloscope. Use of this technique yields a close correlation between ON Semiconductor and customer testing. Unused outputs are loaded with a 50–ohm resistor (100–ohm for MC105XX devices) to ground. The positive supply (V<sub>CC</sub>) should be decoupled from the test board by RF type 25  $\mu F$  capacitors to ground. The V<sub>CC</sub> pins are bypassed to ground with 0.1  $\mu F$ , as is the V<sub>EE</sub> pin.

Additional information on testing MECL 10K and understanding data sheets is found in Application Note AN701/D and the MECL System Design Handbook, HB205/D.

Figure 18 – MECL LOGIC SWITCHING TIME TEST SETUP

## **OPERATIONAL DATA**

#### **POWER SUPPLY CONSIDERATIONS**

MECL circuits are characterized with the  $V_{CC}$  point at ground potential and the  $V_{EE}$  point at -5.2 V. While this MECL convention is not necessarily mandatory, it does result in maximum noise immunity. This is so because any noise induced on the  $V_{EE}$  line is applied to the circuit as a common–mode signal which is rejected by the differential action of the MECL input circuit. Noise induced into the  $V_{CC}$  line is not cancelled out in this fashion. Hence, a good system ground at the  $V_{CC}$  bus is required for best noise immunity. Also, MECL 10H circuits may be operated with  $V_{EE}$  at -4.5 V with a negligible loss of noise immunity.

Power supply regulation which will achieve 10% regulation or better at the device level is recommended. The –5.2 V power supply potential will result in best circuit speed. Other values for VEE may be used. A more negative voltage will increase noise margins at a cost of increased power dissipation. A less negative voltage will have just the opposite effect. (Noise margins and performance specifications of MECL 10H are unaffected by variations in VEE because of the internal voltage regulation.)

On logic cards, a ground plane or ground bus system should be used. A bus system should be wide enough to prevent significant voltage drops between supply and device and to produce a low source inductance.

Although little power supply noise is generated by MECL logic, power supply bypass capacitors are recommended to handle switching currents caused by stray capacitance and asymmetric circuit loading. A parallel combination of a 1.0  $\mu F$  and a 100 pF capacitor at the power entrance to the board, and a 0.01  $\mu F$  low–inductance capacitor between ground and the -5.2 V line every four to six packages, are recommended.

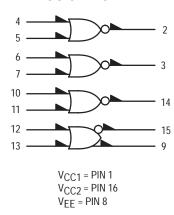

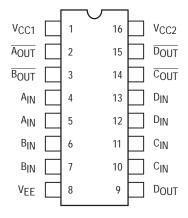

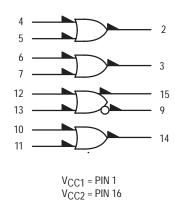

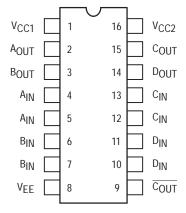

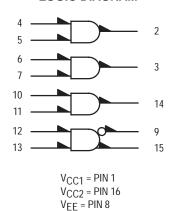

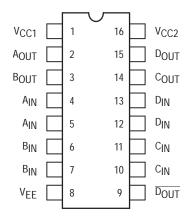

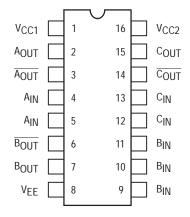

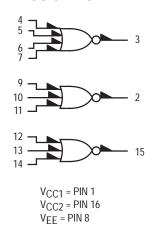

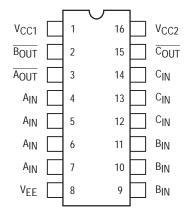

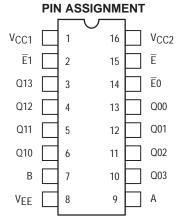

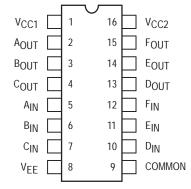

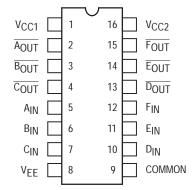

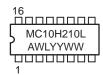

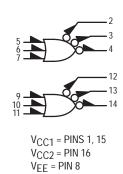

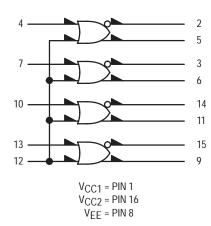

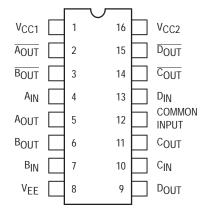

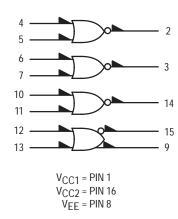

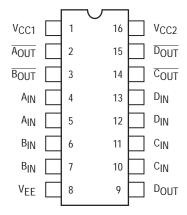

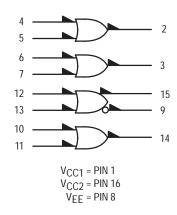

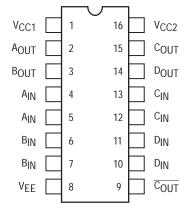

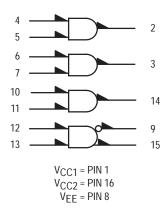

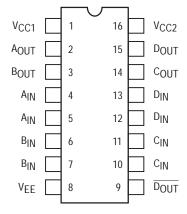

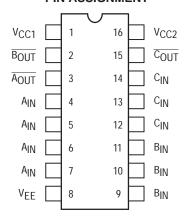

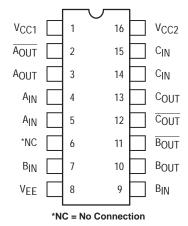

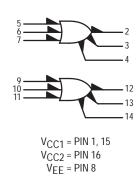

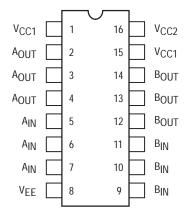

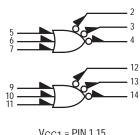

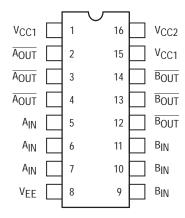

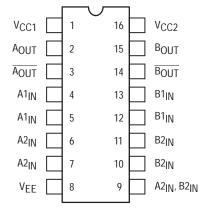

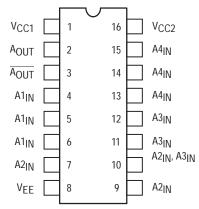

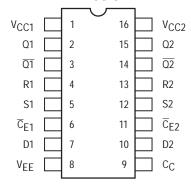

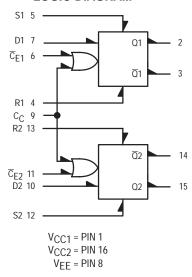

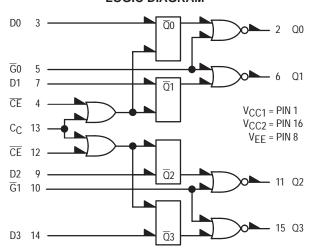

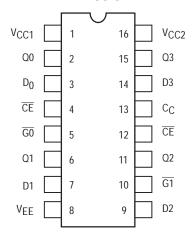

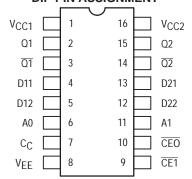

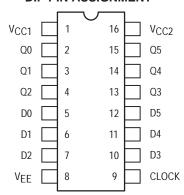

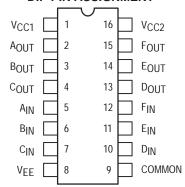

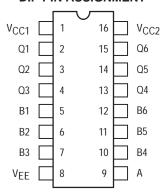

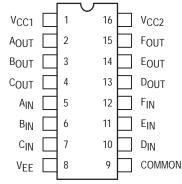

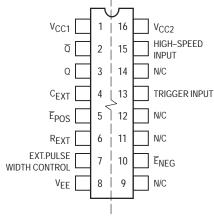

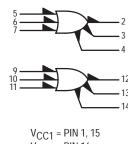

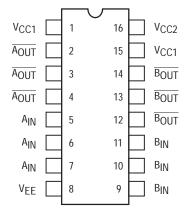

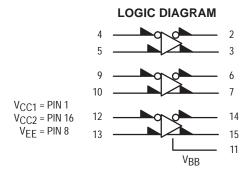

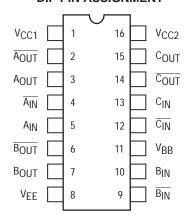

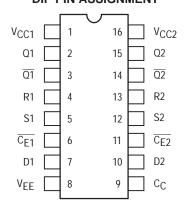

Most MECL 10H, MECL 10K and MECL III circuits have two  $V_{CC}$  leads.  $V_{CC1}$  supplies current to the output transistors and  $V_{CC2}$  is connected to the circuit logic transistors. The separate  $V_{CC}$  pins reduce cross—coupling between individual circuits within a package when the outputs are driving heavy loads. Circuits with large drive capability, similar to the MC10110, have two  $V_{CC1}$  pins. All  $V_{CC}$  pins should be connected to the ground plane or ground bus as close to the package as possible.

For further discussion of MECL power supply considerations to be made in system designing, see MECL System Design Handbook, HB205/D.

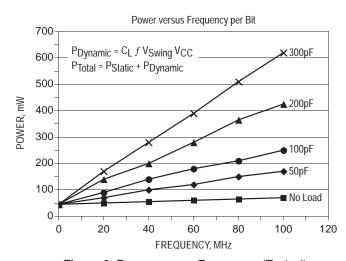

#### **POWER DISSIPATION**

The power dissipation of MECL functional blocks is specified on their respective data sheets. This specification does not include power dissipated in the output devices due to output termination. The omission of internal output pulldown resistors permits the use of external terminations designed to yield best system performance. To obtain total

operating power dissipation of a particular functional block in a system, the dissipation of the output transistor, under load, must be added to the circuit power dissipation.

Table 7 lists the power dissipation in the output transistors plus that in the external terminating resistors, for the more commonly used termination values and circuit configurations. To obtain true package power dissipation, one output–transistor power–dissipation value must be added to the specified package power dissipation for each external termination resistor used in conjunction with that package. To obtain system power dissipation, the stated dissipation in the external terminating resistors must be added as well. Unused outputs draw no power and may be ignored.

Table 7 – AVERAGE POWER DISSIPATION IN OUTPUT CIRCUIT WITH EXTERNAL TERMINATING RESISTORS

| Terminating<br>Resistor Value                              | Output<br>Transistor<br>Power<br>Dissipation<br>(mW) | Terminating Resistor Power Dissipation (mW) |

|------------------------------------------------------------|------------------------------------------------------|---------------------------------------------|

| 150 ohms to -2.0 Vdc                                       | 5.0                                                  | 4.3                                         |

| 100 ohms to -2.0 Vdc                                       | 7.5                                                  | 6.5                                         |

| 75 ohms to -2.0 Vdc                                        | 10                                                   | 8.7                                         |

| 50 ohms to -2.0 Vdc                                        | 15                                                   | 13                                          |

| 2.0 k ohms to VEE                                          | 2.5                                                  | 7.7                                         |

| 1.0 k ohm to VEE                                           | 4.9                                                  | 15.4                                        |

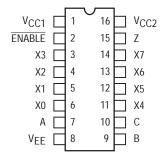

| 680 ohms to VEE                                            | 7.2                                                  | 22.6                                        |